# Waterford Institute of Technology Ireland

Institiúid Teicneolaíochta Phort Láirge

Éire

# A CAN to FlexRay Migration

# Framework

Richard Murphy B.Sc. (Hons)

M.Sc. Thesis

(Supervisor) Frank Walsh B.A., B.A.I., M.Sc.

# Acknowledgments

I would like to thank sincerely the following people, for without their input this thesis would not have been possible.

I would like to thank my supervisor Frank Walsh for his ideas and input especially when things were not going to plan he was always willing to give up his time to discuss any issues. I would also like to thank the group leader, Brendan Jackman for his assistance and input any time it was asked of him. A big thank you must go to Gareth, Rob and Wei Da who helped me any time I asked even while they were busy conducting their own research.

I would like to thank Sumitomo Ystrad. The financial backing of Sumitomo has made this thesis possible. I would like to especially thank Paul, Jim and Eamonn whose hospitality and assistance was second to none during my visits there.

Finally I would like to thank my parents Milo and Kitty who backed me both financially and with encouragement. Without them I would not be where I am now.

| _    |         |   |

|------|---------|---|

| I)ec | aration | ٦ |

|      |         |   |

# **Declaration**

| I Richard Murphy, declare that this thesis is submitted by me in partial fulfilment of the |

|--------------------------------------------------------------------------------------------|

| requirement for the degree M.Sc., is entirely my own work except where otherwise           |

| accredited. It has not at any other time whole or in part been submitted for any other     |

| educational award.                                                                         |

| Signature:  |  |  |

|-------------|--|--|

| Jigilatule. |  |  |

Richard Murphy

9<sup>th</sup> of October 2009

#### **Abstract**

One of the first electronics components used in an automobile was the fuse. Additional features were developed such as engine management systems. These additional features increased the amount of wiring in a wiring harness. This contributed towards the necessity to develop the bus structure in the 1980s. The de-facto bus structure in the automotive industry became CAN (Controller Area Network). By using a bus structure this resulted in less hard wiring being required in the production of an automobile which further lead to a reduction in production cost. CAN is an event-triggered protocol which denotes it is non-deterministic and it has a theoretical bandwidth limit of 1Mbit\s. The practical limit is nearer 500kbit\s. During the 80's and 90's, automotive electronics development increased; this was primarily driven by increased development of safety features such as ABS (Anti-lock Braking System). The increase in the number of features and nodes caused increased traffic on the bus. The CAN protocol will be unable to meet the requirements for the extra applications.

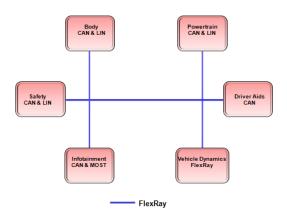

This resulted in the development of FlexRay in 2000 by a consortium originally consisting of amongst others BMW, Daimler Chrysler, Freescale and Philips. This protocol can implement both time-triggered and event-triggered messages, determinism, fault tolerance, redundancy and can operate at 10Mbit\s. Newly developed technologies have high initial costs therefore being initially more expensive than established technologies. This could result in it being financially unworkable to replace a complete automotive bus with FlexRay. FlexRay can possibly be used for mission critical applications such as powertrain applications, while other protocols such as CAN and LIN (Local Interconnect Network) may possibly be used for less critical applications.

The aim of this research is to design and develop a framework that allows the implementation of a CAN application on the FlexRay protocol, without degrading the applications performance.

| Acknow  | rledgmentsi                                        |

|---------|----------------------------------------------------|

| Declara | tionii                                             |

| Abstrac | tiii                                               |

| Table o | f Contentsiv                                       |

| Table o | f Figuresx                                         |

| Table o | f Tablesxv                                         |

| Table o | f Equations xvii                                   |

| Section | I - Thesis Overview1                               |

| 1 Th    | esis Overview:2                                    |

| 1.1     | Problem Specification                              |

| 1.2     | Specified Solution                                 |

| 1.3     | Research Questions                                 |

| 1.4     | Document Layout                                    |

| Section | II - Literature Review7                            |

| 2 Au    | tomotive Networks Review:8                         |

| 2.1     | Introduction                                       |

| 2.2     | Computer Networks                                  |

| 2.3     | Network Function9                                  |

| 2.4     | Network Topologies                                 |

| 2.5     | LAN (Local Area Network) & WAN (Wide Area Network) |

| 2.6     | Communication Protocol                             |

| 2.7     | Automotive Networks History                        |

| 2.8     | Automotive Networks Description                    |

|   | 2.9                             | ECU                                                                                | 20                               |

|---|---------------------------------|------------------------------------------------------------------------------------|----------------------------------|

|   | 2.10                            | Automotive Network Protocols                                                       | 22                               |

|   | 2.11                            | Conclusion                                                                         | 25                               |

|   | 2.12                            | References                                                                         | 27                               |

| 3 | CAN                             | I (Controller Area Network):                                                       | 28                               |

|   | 3.1                             | Introduction                                                                       | 28                               |

|   | 3.2                             | CAN Physical Structure                                                             | 29                               |

|   | 3.3                             | CAN Frame Format                                                                   | 30                               |

|   | 3.4                             | Bus Arbitration                                                                    | 34                               |

|   | 3.5                             | CAN Error Handling                                                                 | 35                               |

|   | 3.6                             | CAN Protocol Features                                                              | 39                               |

|   | 3.7                             | TTCAN (Time-Triggered Controller Area Network) Introduction                        | 40                               |

|   | 3.8                             | Conclusion                                                                         | 43                               |

|   | 3.9                             | References                                                                         | 44                               |

| 4 | Flex                            | Ray:                                                                               | 45                               |

|   | 4.1                             | Introduction                                                                       | 45                               |

|   | 4.2                             | FlexRay Features                                                                   | 46                               |

|   | 4.3                             | FlexRay Cycle Structure                                                            | 48                               |

|   |                                 |                                                                                    |                                  |

|   | 4.4                             | FlexRay Node Structure                                                             |                                  |

|   | 4.4<br>4.5                      | FlexRay Node Structure                                                             | 50                               |

|   |                                 | ·                                                                                  | 50<br>52                         |

|   | 4.5                             | FlexRay Frame Structure                                                            | 50<br>52<br>56                   |

|   | 4.5<br>4.6                      | FlexRay Frame Structure  FlexRay Timing Hierarchy                                  | 50<br>52<br>56<br>58             |

|   | 4.5<br>4.6<br>4.7               | FlexRay Frame Structure  FlexRay Timing Hierarchy  Communication Cycle             | 50<br>52<br>56<br>58<br>62       |

| 5 | 4.5<br>4.6<br>4.7<br>4.8<br>4.9 | FlexRay Frame Structure  FlexRay Timing Hierarchy  Communication Cycle  Conclusion | 50<br>52<br>56<br>58<br>62<br>63 |

|   | 5.2                                          | Distributed Architectures - Introduction | 64                                                   |

|---|----------------------------------------------|------------------------------------------|------------------------------------------------------|

|   | 5.3                                          | Real-Time Operating System (RTOS)        | 66                                                   |

|   | 5.4                                          | OSEK/VDX                                 | 67                                                   |

|   | 5.5                                          | Process Models                           | 70                                                   |

|   | 5.6                                          | Task Scheduling Policies                 | 70                                                   |

|   | 5.7                                          | Task Graphs                              | 74                                                   |

|   | 5.8                                          | Critical Path Analysis (CPA)             | 74                                                   |

|   | 5.9                                          | Task Graph Analysis                      | 77                                                   |

|   | 5.10                                         | Design Process                           | 87                                                   |

|   | 5.11                                         | Conclusion                               | 90                                                   |

|   | 5.12                                         | References                               | 91                                                   |

| 6 | Aut                                          | omotive Network Migration:               | .93                                                  |

|   | 6.1                                          | Automotive Network Migration             | 93                                                   |

|   | 6.2                                          | Introduction                             | 93                                                   |

|   | 6.3                                          | Protocol Migration Requirements          | 93                                                   |

|   | 6.4                                          | Side-by-Side Migration (Using a Gateway) | 95                                                   |

|   |                                              | ,                                        |                                                      |

|   | 6.5                                          | Full Migration                           |                                                      |

|   | 6.5<br>6.6                                   |                                          | 100                                                  |

|   |                                              | Full Migration                           | 100<br>112                                           |

| 7 | 6.6<br>6.7                                   | Full Migration                           | 100<br>112<br>114                                    |

| 7 | 6.6<br>6.7                                   | Full Migration                           | 100<br>112<br>114<br><b>116</b>                      |

| 7 | 6.6<br>6.7<br><b>Lite</b>                    | Full Migration                           | 100<br>112<br>114<br><b>116</b>                      |

|   | 6.6<br>6.7<br><b>Lite</b><br>7.1<br>7.2      | Full Migration                           | 1112<br>1114<br><b>1116</b><br>1116                  |

|   | 6.6<br>6.7<br>Lite<br>7.1<br>7.2<br>ection I | Full Migration                           | 1112<br>1114<br>1116<br>1116<br>1119                 |

| S | 6.6<br>6.7<br>Lite<br>7.1<br>7.2<br>ection I | Full Migration                           | 100<br>112<br>114<br><b>116</b><br>119<br><b>120</b> |

|    | 8.3      | Application Definition                         | 122 |

|----|----------|------------------------------------------------|-----|

|    | 8.4      | CAN Parameter Abstraction                      | 123 |

|    | 8.5      | Migration                                      | 124 |

|    | 8.6      | FlexRay Frame Implementation                   | 124 |

|    | 8.7      | FlexRay Application Configuration              | 125 |

|    | 8.8      | Conclusion                                     | 126 |

| 9  | CAN      | to FlexRay Migration Methodology:              | 127 |

|    | 9.1      | Introduction                                   | 127 |

|    | 9.2      | Framework Development                          | 127 |

|    | 9.3      | System Implementation                          | 129 |

|    | 9.4      | Verification                                   | 130 |

|    | 9.5      | Implementation of Analysis Findings            | 130 |

|    | 9.6      | Applying Framework to a Real-World Application | 131 |

|    | 9.7      | Generic CAN to FlexRay Development             | 131 |

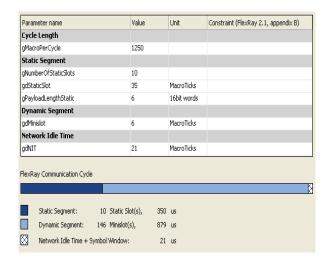

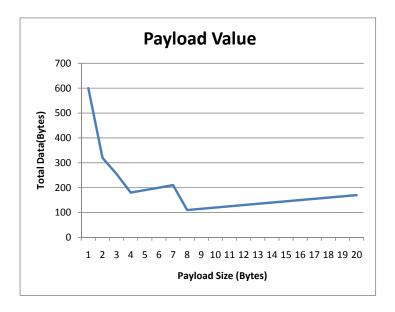

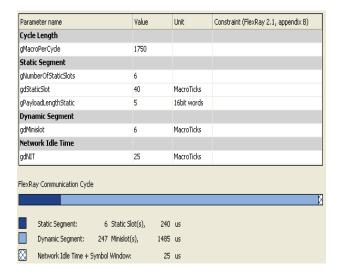

|    | 9.8      | Static Segment Development                     | 132 |

|    | 9.9      | Dynamic Segment Development                    | 140 |

|    | 9.10     | Conclusion                                     | 143 |

|    | 9.11     | References                                     | 147 |

| 1( | ) Dev    | elopment Tools and Applications:               | 148 |

|    | 10.1     | Introduction                                   | 148 |

|    | 10.2     | Hardware                                       | 148 |

|    | 10.3     | Software                                       | 154 |

|    | 10.4     | Conclusion                                     | 169 |

|    | 10.5     | References                                     | 170 |

| Se | ection I | V - Testing & Results                          | 171 |

| 11 | L Syst   | em Model                                       | 172 |

|    | 11.1   | Introduction                                            | 172 |

|----|--------|---------------------------------------------------------|-----|

|    | 11.2   | Traction Control & Adaptive Cruise Control Summary      | 172 |

|    | 11.3   | Application Models                                      | 173 |

|    | 11.4   | Hardware                                                | 178 |

|    | 11.5   | Software                                                | 181 |

|    | 11.6   | Extraction Method                                       | 182 |

|    | 11.7   | Verification of Parameter Consistency                   | 182 |

|    | 11.8   | Validation Check                                        | 183 |

|    | 11.9   | Conclusion                                              | 183 |

|    | 11.10  | References                                              | 184 |

| 12 | 2 Fran | nework Implementation Procedure:                        | 185 |

|    | 12.1   | Introduction                                            | 185 |

|    | 12.2   | Abstract (TC) Implementation (Test Case 1)              | 185 |

|    | 12.3   | Dynamic Segment Verification                            | 197 |

|    | 12.4   | Final Abstract Case Parameters                          | 201 |

|    | 12.5   | Experimental Implementation (ACC) (Test Case 2)         | 202 |

|    | 12.6   | Dynamic Segment Analysis                                | 209 |

|    | 12.7   | Final Experimental Case Parameters                      | 211 |

|    | 12.8   | Verification of Time-Triggered Properties (Test Case 3) | 213 |

|    | 12.9   | Final Practical Case Parameters                         | 219 |

|    | 12.10  | Conclusion                                              | 220 |

|    | 12.11  | References                                              | 222 |

| 13 | 3 Test | Results & Verification:                                 | 223 |

|    | 13.1   | Introduction                                            | 223 |

|    | 13.2   | Test Case 2: ACC Configuration                          | 224 |

|    | 13.3   | CAN Results                                             | 225 |

| 13.4      | FlexRay Results                                        | 245 |

|-----------|--------------------------------------------------------|-----|

| 13.5      | Discussion of Results                                  | 272 |

| 13.6      | Test Case 3: Verification of Time-Triggered Properties | 277 |

| 13.7      | Conclusion                                             | 282 |

| Section ' | V - Conclusion                                         | 283 |

| 14 Cor    | nclusion:                                              | 284 |

| 14.1      | Research Summary                                       | 284 |

| 14.2      | Summary of Testing and Results                         | 285 |

| 14.3      | Research Questions                                     | 287 |

| 14.4      | Areas for Future Research                              | 288 |

| Section ' | VI- Appendices                                         | 290 |

| Appendi   | ix A                                                   | I   |

| 14.5      | Published Material                                     | 1   |

| Appendi   | ix B                                                   | II  |

| 14.6      | Bibliography                                           | 11  |

| Appendi   | ix C                                                   | v   |

| 14.7      | Calculations                                           | V   |

| FIGURE 2-1: A SIMPLE NETWORK EXAMPLE                                             | 9         |

|----------------------------------------------------------------------------------|-----------|

| FIGURE 2-2: BUS TOPOLOGY                                                         | 10        |

| FIGURE 2-3: STAR TOPOLOGY                                                        | 11        |

| FIGURE 2-4: RING TOPOLOGY                                                        | 12        |

| FIGURE 2-5: MESH TOPOLOGY                                                        | 12        |

| FIGURE 2-6: TCP/IP MODEL                                                         | 14        |

| FIGURE 2-8: COST V'S DATA RATE OF DIFFERENT AUTOMOTIVE PROTOCOLS                 | 17        |

| FIGURE 2-9: BASIC NETWORK CONFIGURATION                                          | 18        |

| FIGURE 2-10: POINT-TO-POINT NETWORK                                              | 19        |

| FIGURE 2-11: A BASIC NODE COMPRISING OF A SENSOR AND ECU                         | 20        |

| FIGURE 2-12: MICROPROCESSOR BLOCK DIAGRAM                                        | 21        |

| FIGURE 2-13: TIME TRIGGERED SLOTS ON A NETWORK                                   | 24        |

| FIGURE 3-1: CAN'S RELATION TO THE OSI MODEL                                      | 29        |

| FIGURE 3-2: TERMINATING RESISTORS (TO STOP REFLECTION)                           | 30        |

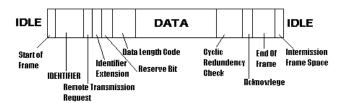

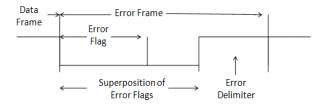

| FIGURE 3-3: CAN STANDARD FRAME FORMAT                                            | 31        |

| FIGURE 3-4: CAN EXTENDED FORMAT                                                  | 31        |

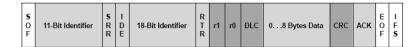

| FIGURE 3-5: REMOTE FRAME                                                         | 32        |

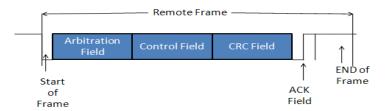

| FIGURE 3-6: ERROR FRAME FORMAT                                                   | 33        |

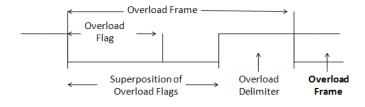

| FIGURE 3-7: OVERLOAD FRAME FORMAT                                                | 33        |

| FIGURE 3-8: ARBITRATION PROCESS                                                  | 35        |

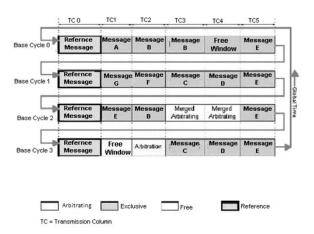

| FIGURE 3-9: TTCAN MATRIX CYCLE                                                   | 41        |

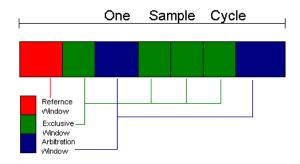

| FIGURE 3-10: TTCAN SAMPLE WINDOW TIME                                            | 42        |

| FIGURE 4-1: POSSIBLE FLEXRAY IMPLEMENTATION                                      | 46        |

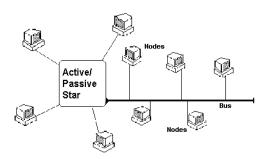

| FIGURE 4-2: STAR AND BUS TOPOLOGY COMBINATION                                    | 48        |

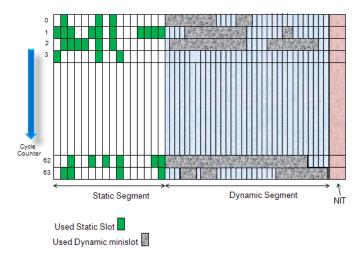

| FIGURE: 4-3: FLEXRAY CYCLE STRUCTURE                                             | 49        |

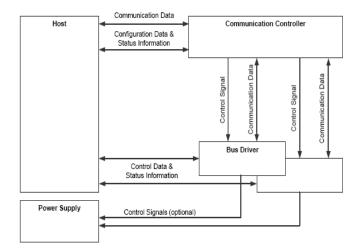

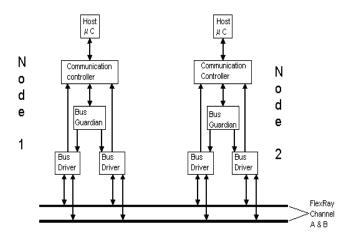

| FIGURE 4-4: NODE ARCHITECTURE (CONSORTIUM, 2005)                                 | 50        |

| FIGURE 4-5: NODE COMPONENTS                                                      | 51        |

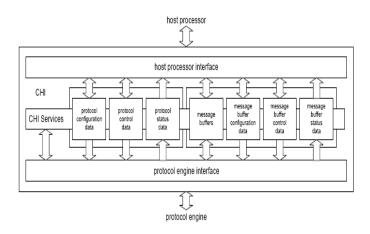

| FIGURE 4-6: ROLE THE CHI HAS IN THE PE INTERACTING WITH THE HOST PROCESSOR (CONS | ORTIUM,   |

| 2005)                                                                            | 52        |

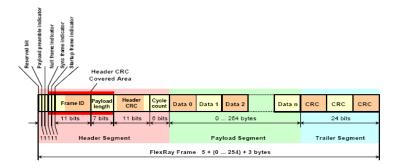

| FIGURE 4-7: FRAME FORMAT (CONSORTIUM, 2005)                                      | 53        |

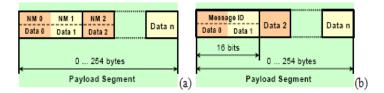

| FIGURE 4-8: PAYLOAD SEGMENT CONTAINING THE NETWORK MANAGEMENT (NM) VECTOR        | & MESSAGE |

| ID                                                                               | 54        |

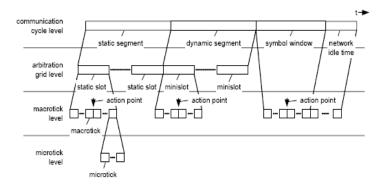

| FIGURE 4-9: FLEXRAY TIMING HIERARCHY (CONSORTIUM, 2005)                          | 57        |

| FIGURE 4-10: POSSIBLE FLEXRAY FRAME CYCLE CONFIGURATION                | 58  |

|------------------------------------------------------------------------|-----|

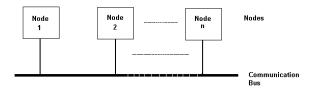

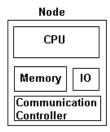

| FIGURE 5-1: BASIC DISTRIBUTED ARCHITECTURE                             | 65  |

| FIGURE 5-2: GENERAL NODE PROPERTIES                                    | 65  |

| FIGURE 5-3: OSEK MODEL V'S OSI 7 LAYER MODEL                           | 69  |

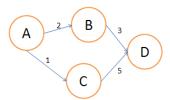

| FIGURE 5-4: BASIC TASK GRAPH                                           | 70  |

| FIGURE 5-5: SIMPLE ACTIVITY CONFIGURATION                              | 75  |

| FIGURE 5-6: SAMPLE PROCESS MODEL                                       | 76  |

| FIGURE: 5-7: ALTERNATIVE ACTIVITY TASK CONFIGURATIONS                  | 76  |

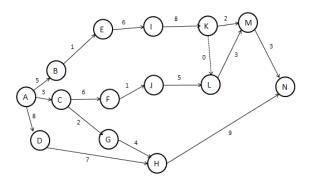

| FIGURE: 5-8: SAMPLE COMPLEX CPA MODEL                                  | 77  |

| FIGURE: 5-9: TASK CONTENTS                                             | 77  |

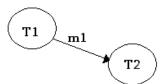

| FIGURE: 5-10: TWO TASKS, T1 & T2, CONNECTED BY A MESSAGE M1            | 78  |

| FIGURE 5-11: TASK T1S RELEASE AND DEADLINE PARAMETERS                  | 78  |

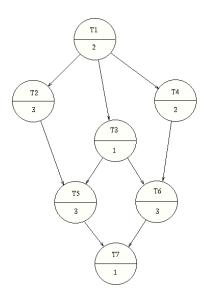

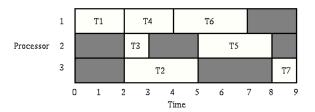

| FIGURE 5-12: TASK GRAPH EXAMPLE (HURLEY, 1994)                         | 79  |

| FIGURE 5-13: GANTT CHART FOR TASKS IN FIGURE 5-12 (HURLEY, 1994)       | 79  |

| FIGURE 5-14: FOUR PHASES OF A TASKS EXECUTION                          | 83  |

| FIGURE 6-1: PROTOCOL COMMON FUNCTIONALITY                              | 94  |

| FIGURE 6-2: CONVERTER BETWEEN TWO DIFFERENT PROTOCOLS                  | 94  |

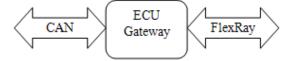

| FIGURE 6-3: EXAMPLE GATEWAY USAGE                                      | 95  |

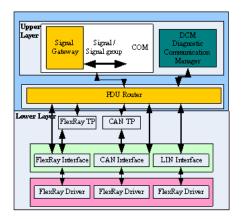

| FIGURE 6-4: AUTOSAR GATEWAY STRUCTURE                                  | 97  |

| FIGURE 6-5: FLOW CHART CONVERTING FLEXRAY TO CAN (SUK-HYUN SEOL, 2006) | 99  |

| FIGURE 6-6: ALGORITHM FOR GENERATING AN INDIVIDUAL (SHAN DING, 2005)   | 103 |

| FIGURE 6-7: NETWORK TOPOLOGY SYNTHESIS ALGORITHM (ALOUL, 2005)         | 106 |

| FIGURE 6-8: DESIGN HEURISTIC (TRAIAN POP, 2002)                        | 107 |

| FIGURE 6-9: TT AND DYN SCHEDULABILITY ALGORITHMS (TRAIAN POP, 2006)    | 107 |

| FIGURE 6-10: OPTIMISED BUS CONFIGURATION ALGORITHM (TRAIAN POP, 2007)  | 108 |

| FIGURE 6-11: GLOBAL SCHEDULING ALGORITHM (TRAIAN POP, 2006)            | 110 |

| FIGURE 8-1: FRAMEWORK DEVELOPMENT STAGES                               | 122 |

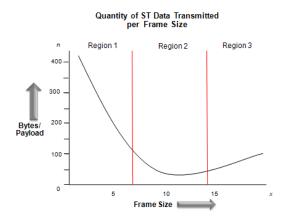

| FIGURE 9-1: ST FRAME DATA GRAPH PROFILE                                | 137 |

| FIGURE 9-2: ILLUSTRATION OF PERIODICITY AND DISTANCE CONSTRAINT        | 139 |

| FIGURE 9-3: ST SCHEDULING ALGORITHM                                    | 145 |

| FIGURE 9-4: DYN SCHEDULING ALGORITHM                                   | 146 |

| FIGURE 9-5: FLEXRAY EXTRACTION PARAMETERS                              | 146 |

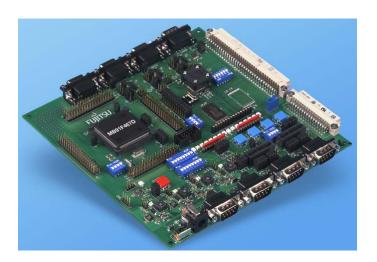

| FIGURE 10-1: FUJITSU SK-91F467D FLEXRAY STARTER KIT                    | 150 |

| FIGURE 10-2: FLEXRAY PHYSICAL LAYER DRIVER MODULE                      | 151 |

| FIGURE 10-3: VN3600 FLEXRAY INTERFACE                                  | 152 |

| FIGURE 10-4: CANCARDXL                                                 | 153 |

| FIGURE 10-5: FLEXRAY PASSIVE STAR                                      | 153 |

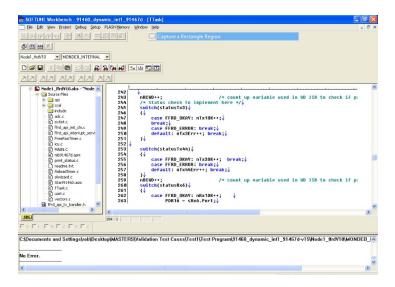

| FIGURE 10-6: SOFTUNE WORKBENCH V6                                      | 154 |

| FIGURE 10-7: FME FR FLASH PROGRAMMER                                        | 155 |

|-----------------------------------------------------------------------------|-----|

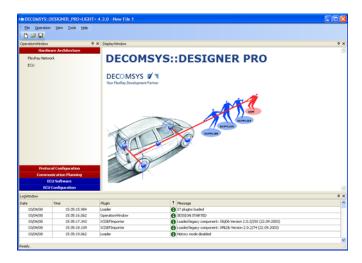

| FIGURE 10-8: DECOMSYS::DESIGNER PRO                                         | 156 |

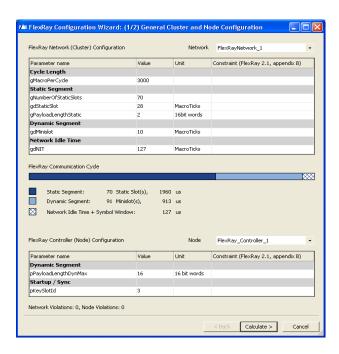

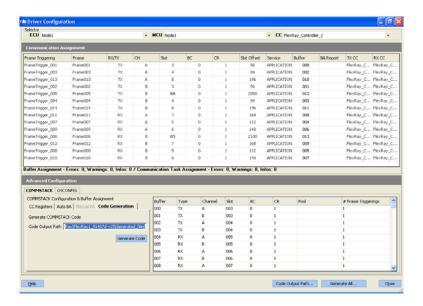

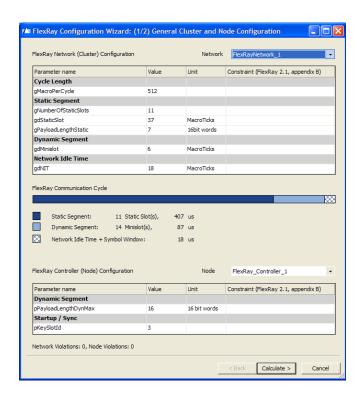

| FIGURE 10-9: FLEXRAY NODE AND CLUSTER CONFIGURATION                         | 157 |

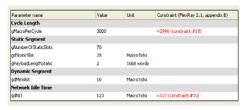

| FIGURE 10-10: CONSTRAINT VIOLATION                                          | 157 |

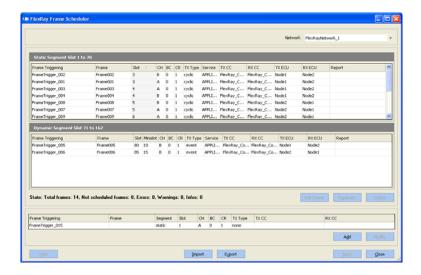

| FIGURE 10-11: SAMPLE FRAME SCHEDULE                                         | 159 |

| FIGURE 10-12: ECU CONFIGURATION SCREEN                                      | 160 |

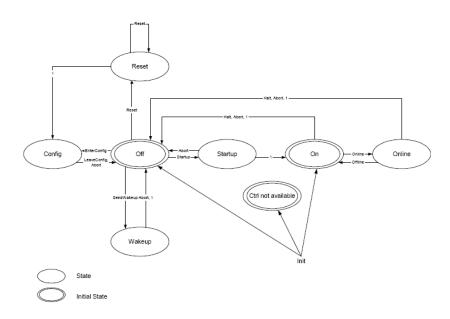

| FIGURE 10-13: COMMSTACK FLEXRAY CONTROLLER STATE MACHINE (EGGENBAUER, 2006) | 161 |

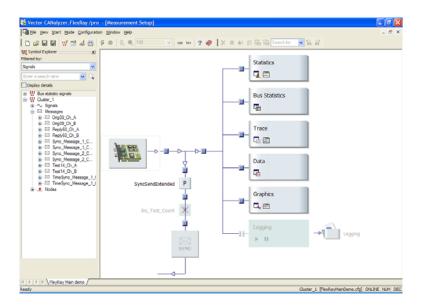

| FIGURE 10-14: FLEXRAY SAMPLE FLOW DIAGRAM                                   | 167 |

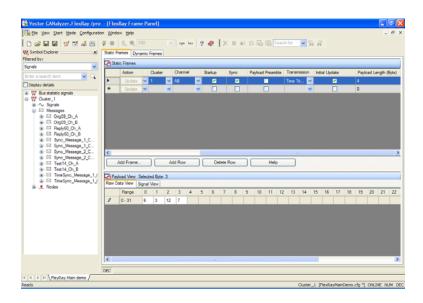

| FIGURE 10-15: FLEXRAY FRAME PANEL                                           | 168 |

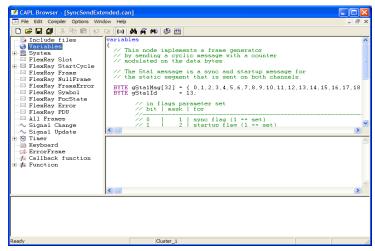

| FIGURE 10-16: CAPL BROWSER PANEL                                            | 168 |

| FIGURE 11-1: ABSTRACT IMPLEMENTATION STAGES                                 | 173 |

| FIGURE 11-2: TRACTION CONTROL TASK GRAPH MODEL                              | 174 |

| FIGURE 11-3: ACC TASK GRAPH REPRESENTATION                                  | 176 |

| FIGURE 11-4: ACC BLOCK DIAGRAM REPRESENTATION                               | 177 |

| FIGURE 11-5 : TEST CASE THREE TASK GRAPH CONFIGURATION                      | 178 |

| FIGURE 11-6: CAN PHYSICAL TEST CONFIGURATION                                | 180 |

| FIGURE 11-7: FLEXRAY PHYSICAL TEST CONFIGURATION                            | 181 |

| FIGURE 12-1: FIRST FRAMEWORK DEVELOPMENT STAGE                              | 186 |

| FIGURE 12-2 : MIGRATION STEP TWO                                            | 186 |

| FIGURE 12-3: FRAMEWORK DEVELOPMENT STAGE THREE                              | 187 |

| FIGURE 12-4: PATH P4 ON THE TRACTION CONTROL MODEL                          | 190 |

| FIGURE 12-5: FLOWCHART DEVELOPMENT STAGE FOUR                               | 192 |

| FIGURE 12-6 : STAGE FIVE DEVELOPMENT                                        | 193 |

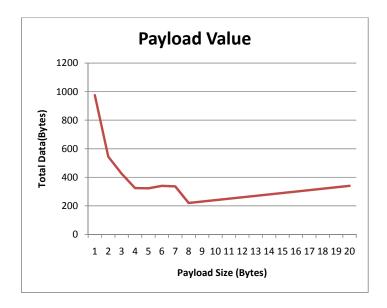

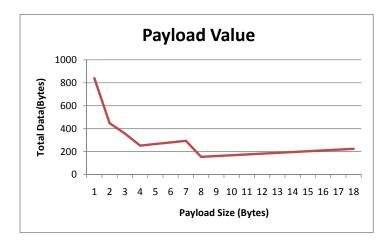

| FIGURE 12-7: PAYLOAD GRAPH PROFILE                                          | 195 |

| FIGURE 12-8: CONFIGURED ABSTRACT PARAMETERS                                 | 201 |

| FIGURE 12-9: PAYLOAD GRAPH PROFILE                                          | 207 |

| FIGURE 12-10: CONFIGURED ABSTRACT PARAMETERS                                | 212 |

| FIGURE 12-11: FRAMEWORK DEVELOPMENT STAGE SIX                               | 212 |

| FIGURE 12-12: PATH THROUGH TASK GRAPH                                       | 214 |

| FIGURE 12-13: PAYLOAD GRAPH PROFILE                                         | 217 |

| FIGURE 12-14: CONFIGURED ABSTRACT PARAMETERS                                | 220 |

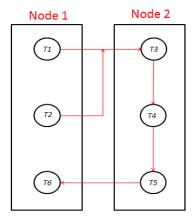

| FIGURE 13-1: STANDARD TASK NODAL ASSIGNMENT                                 | 224 |

| FIGURE 13-2: MINIMAL TASK NODAL ASSIGNMENT                                  | 225 |

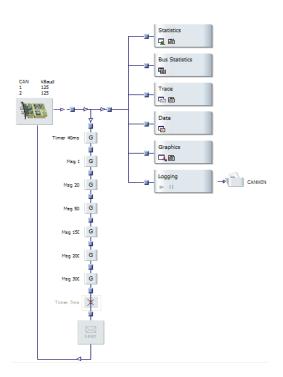

| FIGURE 13-3: STAGE SEVEN OF THE FRAMEWORK DEVELOPMENT                       | 225 |

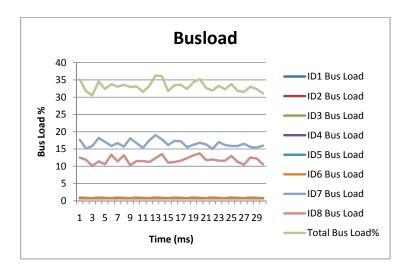

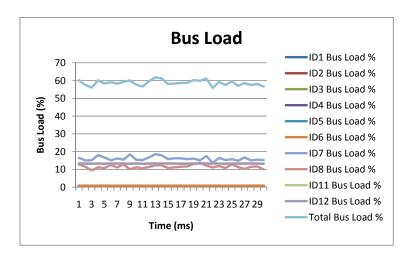

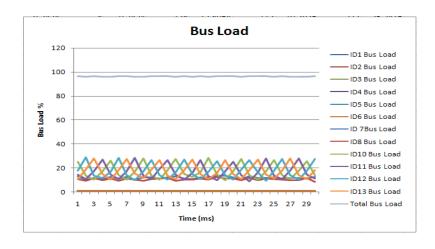

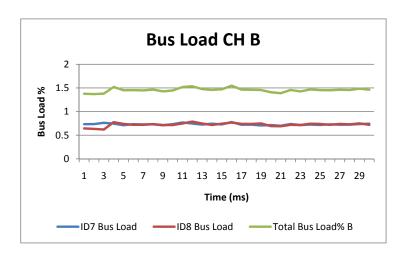

| FIGURE 13-4: NORMAL BUSLOAD                                                 | 227 |

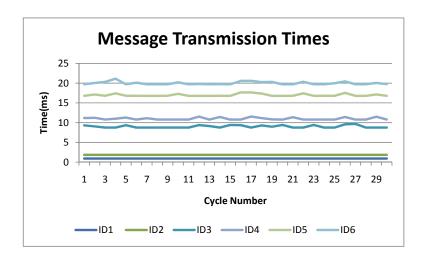

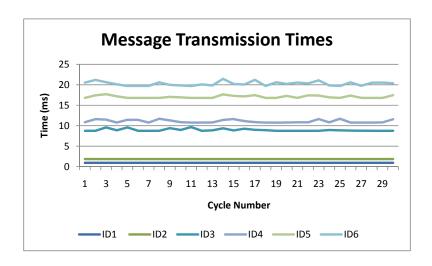

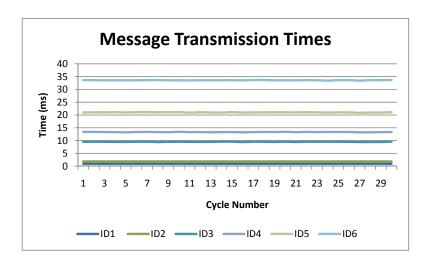

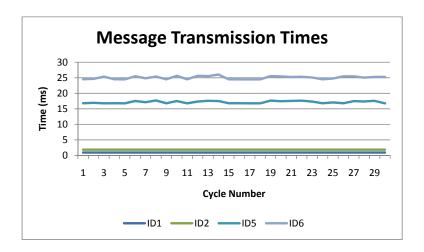

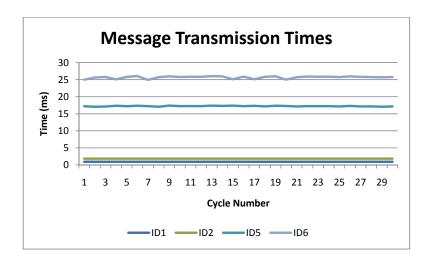

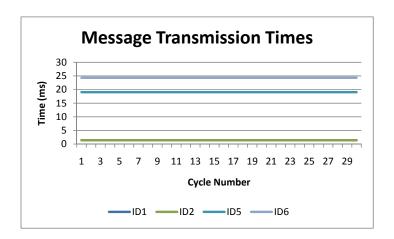

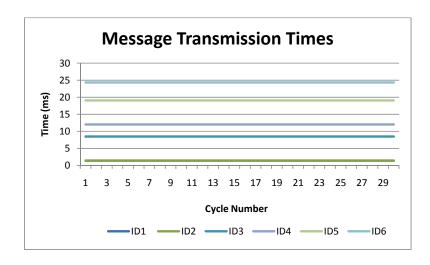

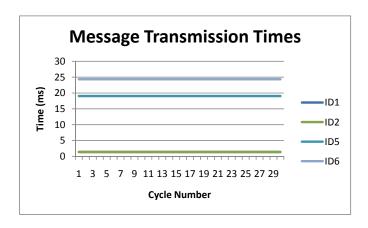

| FIGURE 13-5: MESSAGE TRANSMISSION TIMES AT NORMAL LOAD                      | 228 |

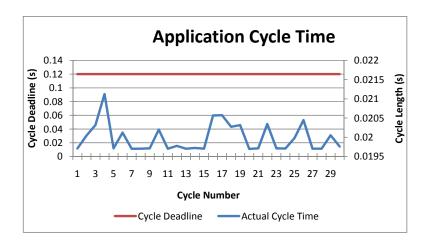

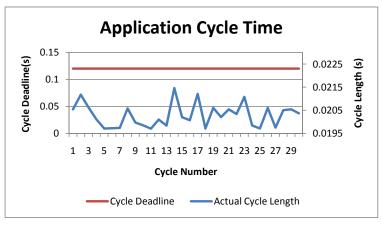

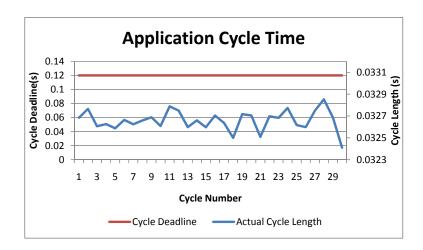

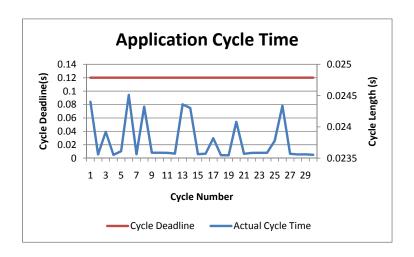

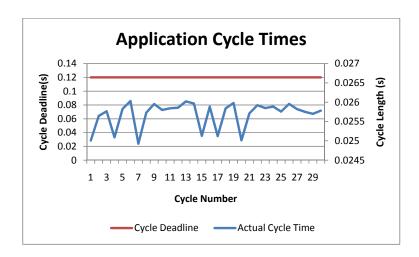

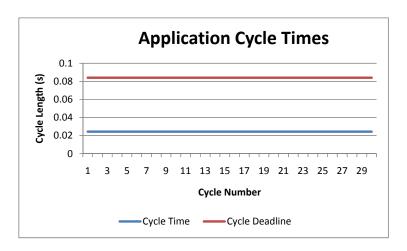

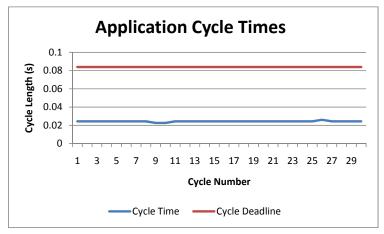

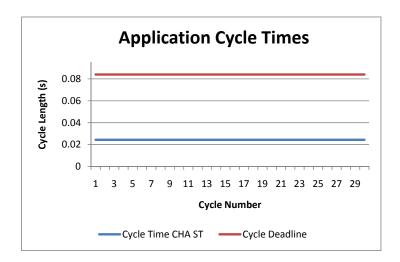

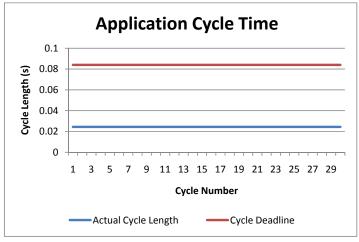

| FIGURE 13-6: APPLICATION CYCLE TIMES AT NORMAL LOAD                         | 229 |

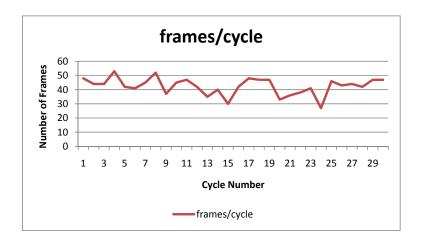

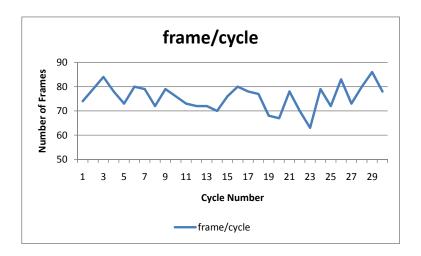

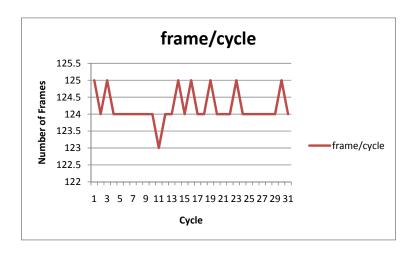

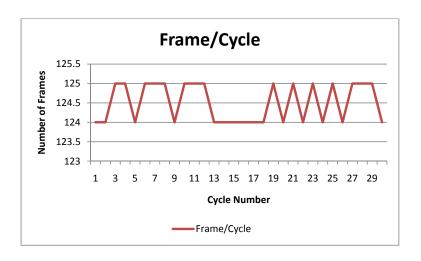

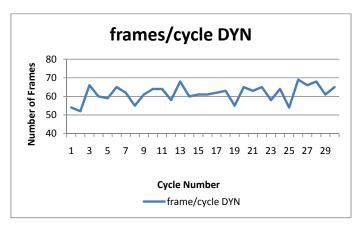

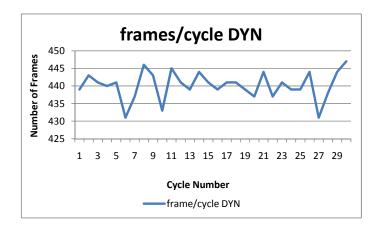

| FIGURE 13-7: NUMBER OF FRAMES PER CYCLE AT NORMAL LOAD                      | 230 |

| FIGURE 13-8: 60% BUSLOAD                                    | . 231 |

|-------------------------------------------------------------|-------|

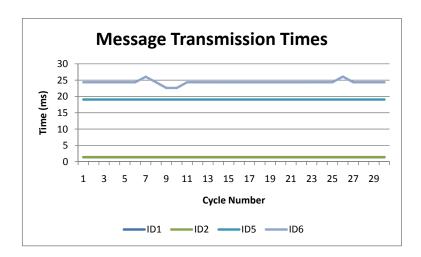

| FIGURE 13-9: MESSAGE TRANSMISSION TIMES AT 60% LOAD         | . 232 |

| FIGURE 13-10: APPLICATION CYCLE TIMES AT 60% LOAD           | . 232 |

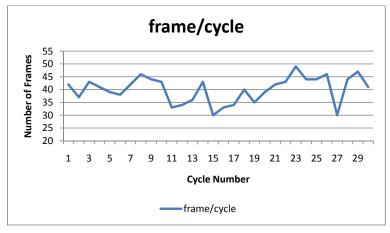

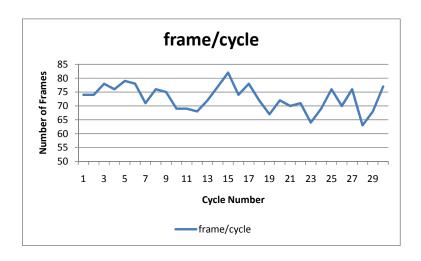

| FIGURE 13-11: NUMBER OF FRAMES PER CYCLE AT 60% LOAD        | . 233 |

| FIGURE 13-12: MAXIMUM BUSLOAD                               | . 234 |

| FIGURE 13-13: MESSAGE TRANSMISSION TIMES AT MAXIMUM LOAD    | . 235 |

| FIGURE 13-14: APPLICATION CYCLE TIMES AT MAXIMUM LOAD       | . 236 |

| FIGURE 13-15: NUMBER OF FRAMES PER CYCLE AT MAXIMUM LOAD    | . 237 |

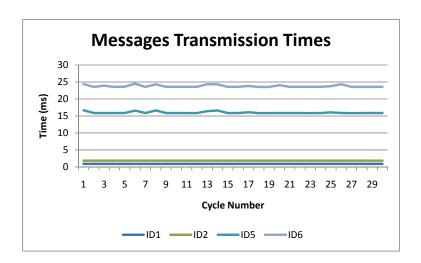

| FIGURE 13-16: MESSAGE TRANSMISSION TIMES AT NORMAL LOAD     | . 238 |

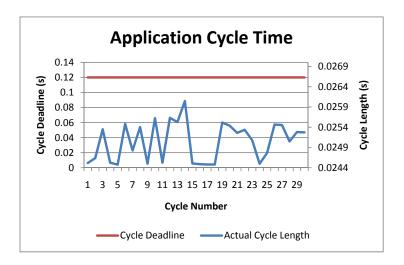

| FIGURE 13-17: APPLICATION CYCLE TIMES AT NORMAL LOAD        | . 239 |

| FIGURE 13-18: NUMBER OF FRAMES PER CYCLE AT NORMAL LOAD     | . 239 |

| FIGURE 13-19: MESSAGE TRANSMISSION TIMES AT 60% LOAD        | . 240 |

| FIGURE 13-20: APPLICATION CYCLE TIMES AT 60% LOAD           | . 241 |

| FIGURE 13-21: NUMBER OF FRAMES PER CYCLE AT 60% LOAD        | . 242 |

| FIGURE 13-22: MESSAGE TRANSMISSION TIMES AT MAXIMUM LOAD    | . 243 |

| FIGURE 13-23: APPLICATION CYCLE TIMES AT MAXIMUM LOAD       | . 244 |

| FIGURE 13-24: NUMBER OF FRAMES PER CYCLE AT MAXIMUM LOAD    | . 245 |

| FIGURE 13-25: NO REDUNDANCY NORMAL BUSLOAD CH A             | . 247 |

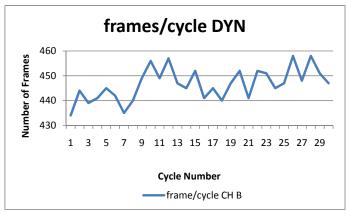

| FIGURE 13-26: NO REDUNDANCY NORMAL BUSLOAD CH B             | . 248 |

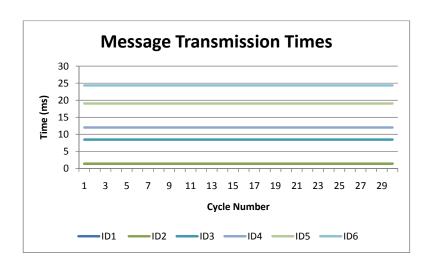

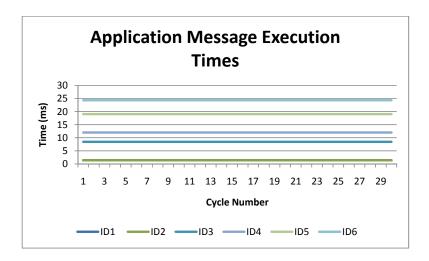

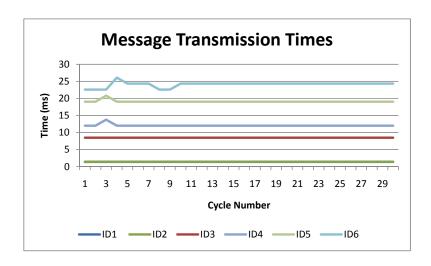

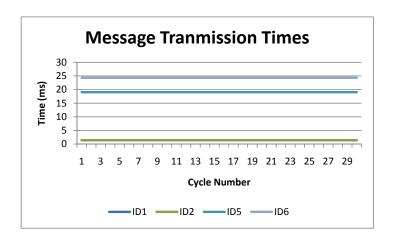

| FIGURE 13-27: MESSAGE TRANSMISSION TIMES NORMAL LOAD        | . 249 |

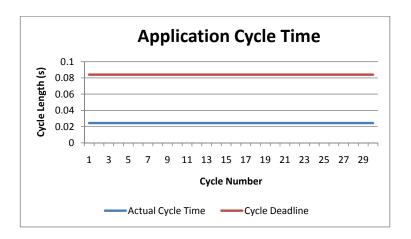

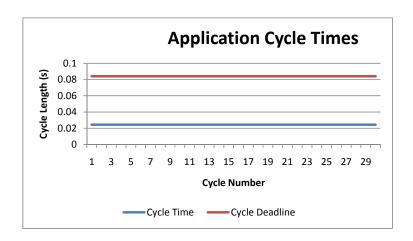

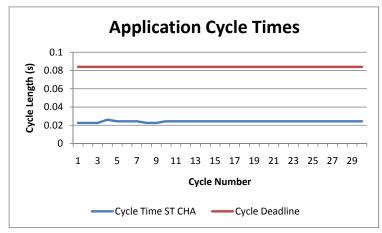

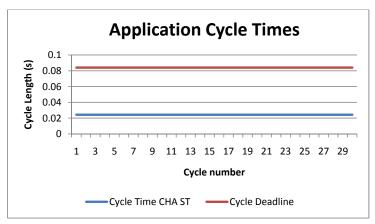

| FIGURE 13-28: APPLICATION CYCLE TIMES NORMAL LOAD           | . 250 |

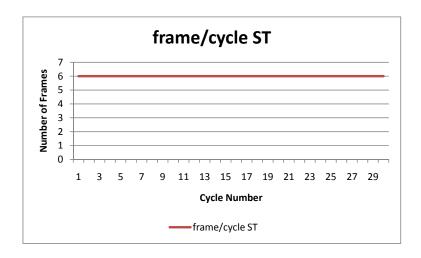

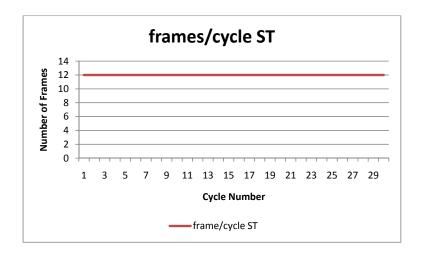

| FIGURE 13-29: NUMBER OF ST FRAMES PER CYCLE (NO REDUNDANCY) | . 251 |

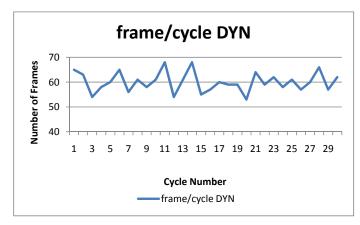

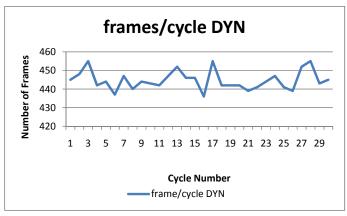

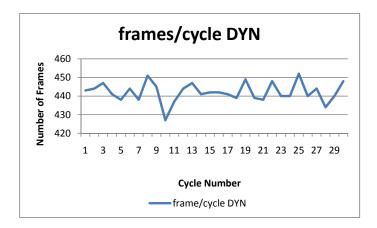

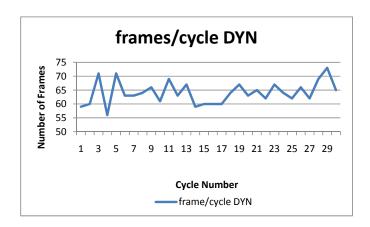

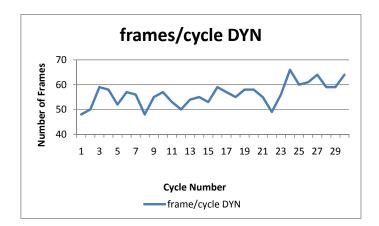

| FIGURE 13-30: NUMBER OF DYN FRAMES PER CYCLE NORMAL LOAD    | . 251 |

| FIGURE 13-31: MESSAGE TRANSMISSION TIMES HIGH DATA RATE     | . 253 |

| FIGURE 13-32: APPLICATION CYCLE TIMES HIGH DATA RATE        | . 254 |

| FIGURE 13-33: NUMBER OF DYN FRAMES PER CYCLE HIGH DATA RATE | . 254 |

| FIGURE 13-34: MESSAGE TRANSMISSION TIMES AT NORMAL LOAD     | . 256 |

| FIGURE 13-35: APPLICATION CYCLE TIMES AT NORMAL LOAD        | . 257 |

| FIGURE 13-36: NUMBER OF DYN FRAMES PER CYCLE AT NORMAL LOAD | . 257 |

| FIGURE 13-37: MESSAGE TRANSMISSION TIMES HIGH DATA RATE     | . 259 |

| FIGURE 13-38: APPLICATION CYCLE TIMES HIGH DATA RATE        | . 259 |

| FIGURE 13-39: NUMBER OF DYN FRAMES PER CYCLE HIGH DATA RATE | . 260 |

| FIGURE 13-40: MESSAGE TRANSMISSION TIMES AT NORMAL LOAD     | . 261 |

| FIGURE 13-41: APPLICATION CYCLE TIMES AT NORMAL LOAD        | . 262 |

| FIGURE 13-42: NUMBER OF DYN FRAMES PER CYCLE AT NORMAL LOAD | . 263 |

| FIGURE 13-43: MESSAGE TRANSMISSION TIMES HIGH DATA RATE     | . 265 |

| FIGURE 13-44: APPLICATION CYCLE TIMES HIGH DATA RATE        | . 265 |

| FIGURE 13-45: NUMBER OF ST FRAMES PER CYCLE HIGH DATA RATE  | 266   |

| FIGURE 13-46: NUMBER OF DYN FRAMES PER CYCLE HIGH DATA RATE  | 266 |

|--------------------------------------------------------------|-----|

| FIGURE 13-47: MESSAGE TRANSMISSION TIMES AT NORMAL LOADS     | 268 |

| FIGURE 13-48: APPLICATION CYCLE TIMES AT NORMAL LOADS        | 268 |

| FIGURE 13-49: NUMBER OF DYN FRAMES PER CYCLE AT NORMAL LOADS | 269 |

| FIGURE 13-50: MESSAGE TRANSMISSION TIMES HIGH DATA RATE      | 271 |

| FIGURE 13-51: APPLICATION CYCLE TIMES HIGH DATA RATE         | 271 |

| FIGURE 13-52: NUMBER OF DYN FRAMES PER CYCLE HIGH DATA RATE  | 272 |

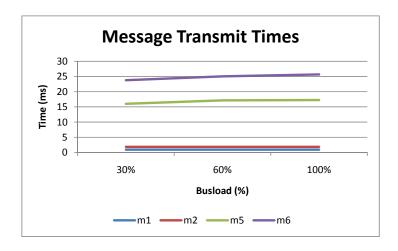

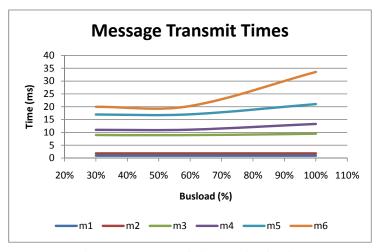

| FIGURE 13-53: MESSAGE TRANSMIT TIMES (MINIMAL CONFIGURATION) | 275 |

| FIGURE 13-54: MESSAGE TRANSMIT TIMES (NORMAL CONFIGURATION)  | 275 |

| FIGURE 13-55: CAN CONFIGURATION TEST THREE                   | 279 |

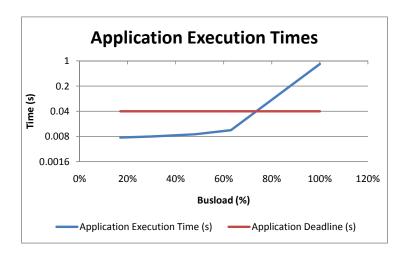

| FIGURE 13-56: GRAPH OF CAN APPLICATION EXECUTION TIMES       | 280 |

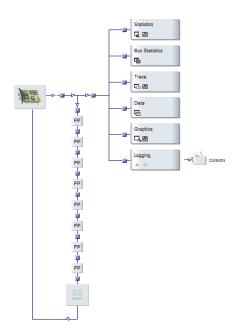

| FIGURE 13-57: FLEXRAY CONFIGURATION TEST THREE               | 281 |

# **Table of Tables**

| TABLE 3-1: CAN ERROR STATES                            | 38  |

|--------------------------------------------------------|-----|

| TABLE 6-1: EXAMPLE CAN NETWORK                         | 111 |

| TABLE 10-1: OFF STATE                                  | 162 |

| TABLE 10-2: START-UP STATE                             | 163 |

| TABLE 10-3: ON STATE                                   | 164 |

| TABLE 10-4: ONLINE STATE                               | 164 |

| TABLE 10-5: CONFIGURATION STATE                        | 165 |

| TABLE 10-6: RESET STATE                                | 165 |

| TABLE 10-7: WAKEUP STATE                               | 165 |

| TABLE 10-8: ANALYSIS FUNCTION BLOCK OVERVIEW           | 166 |

| TABLE 11-1: TRACTION CONTROL TASK FUNCTIONS            | 174 |

| TABLE 11-2: ADAPTIVE CRUISE CONTROL TASK FUNCTIONS     | 175 |

| TABLE 12-1: PARAMETER $C_M \& J_M$ IDENTIFICATION      | 188 |

| TABLE 12-2: $W_M$ FIVE ITERATIONS OF THE QUEUING DELAY | 189 |

| TABLE 12-3: WORST CASE RESPONSE TIME                   | 189 |

| TABLE 12-4: OBTAINING SLACK                            | 190 |

| TABLE 12-5: TASK GRAPH PARAMETERS                      | 191 |

| TABLE 12-6: FINAL TASK GRAPH PARAMETERS                | 191 |

| TABLE 12-7: MESSAGE DEADLINES                          | 192 |

| TABLE 12-8: PAYLOAD CALCULATIONS                       | 194 |

| TABLE 12-9: INITIAL DYNAMIC DATA                       | 197 |

| TABLE 12-10: DYNAMIC COMMUNICATION TIME                | 198 |

| TABLE 12-11: Δ <sub>M</sub> PARAMETERS                 | 199 |

| TABLE 12-12: W <sub>M</sub> (T) PARAMETER              | 200 |

| TABLE 12-13: DYNAMIC RESPONSE TIMES                    | 200 |

| TABLE 12-14: CAN INITIAL PARAMETERS                    | 203 |

| TABLE 12-15: OBTAINING SLACK PARAMETER                 | 203 |

| TABLE 12-16: TASK GRAPH PARAMETERS                     | 204 |

| TABLE 12-17: FINAL TASK GRAPH PARAMETERS               | 204 |

| TABLE 12-18: MESSAGE DEADLINES                         | 205 |

| TABLE 12-19: PAYLOAD CALCULATIONS                      | 206 |

| TABLE 12-20: APERIODIC CAN DATA                        | 210 |

| TABLE 12-21: Δ <sub>M</sub> PARAMETERS                 | 210 |

| TABLE 12-22: W <sub>M</sub> (T) PARAMETER              | 211 |

# Table of Tables

| TABLE 12-23: DYNAMIC RESPONSE TIMES                           | . 211 |

|---------------------------------------------------------------|-------|

| TABLE 12-24: CAN INITIAL PARAMETERS TEST CASE THREE           | . 213 |

| TABLE 12-25: OBTAINING SLACK PARAMETER                        | . 214 |

| TABLE 12-26: TASK GRAPH PARAMETERS                            | . 215 |

| TABLE 12-27: FINAL TASK GRAPH PARAMETERS                      | . 215 |

| TABLE 12-28: MESSAGE DEADLINES                                | . 216 |

| TABLE 12-29: PAYLOAD CALCULATIONS                             | . 216 |

| TABLE 13-1: NORMAL BUSLOAD                                    | . 227 |

| TABLE 13-2: MESSAGE DEADLINES                                 | . 228 |

| TABLE 13-3: 60% BUSLOAD                                       | . 230 |

| TABLE 13-4: MAXIMUM BUSLOAD                                   | . 234 |

| TABLE 13-5: MESSAGE DELAYS                                    | . 235 |

| TABLE 13-6: NORMAL BUSLOAD                                    | . 237 |

| TABLE 13-7: 60% BUSLOAD                                       | . 240 |

| TABLE 13-8: MAXIMUM BUSLOAD                                   | . 242 |

| TABLE 13-9: MESSAGE DELAYS                                    | . 244 |

| TABLE 13-10: STANDARD BUSLOAD                                 | . 247 |

| TABLE 13-11: REVISED FLEXRAY MESSAGE DEADLINES                | . 248 |

| TABLE 13-12: HIGH DATA RATE BUSLOAD                           | . 252 |

| TABLE 13-13: NORMAL BUSLOAD                                   | . 255 |

| TABLE 13-14: HIGH DATA RATE BUSLOAD                           | . 258 |

| TABLE 13-15: NORMAL BUSLOAD                                   | . 261 |

| TABLE 13-16: HIGH DATA RATE BUSLOAD                           | . 264 |

| TABLE 13-17: NORMAL BUSLOAD                                   | . 267 |

| TABLE 13-18: HIGH DATA RATE BUSLOAD                           | . 270 |

| TABLE 13-19: NUMBER OF CAN FRAMES PER SECOND                  | . 273 |

| TABLE 13-20: NUMBER OF FLEXRAY FRAMES PER SECOND              | . 273 |

| TABLE 13-21: ACC CAN APPLICATION CYCLE STANDARD DEVIATION     | . 276 |

| TABLE 13-22: ACC FLEXRAY APPLICATION CYCLE STANDARD DEVIATION | . 277 |

| TABLE 13-23: APPLICATION IDS                                  | . 278 |

| TABLE 12.24. ADDITION EVECTITION TIMES                        | 270   |

# **Table of Equations**

| EQUATION 5-1: UTILISATION BOUND                                                           | 72  |

|-------------------------------------------------------------------------------------------|-----|

| EQUATION 5-2: WCET                                                                        | 80  |

| EQUATION 5-3: MESSAGE DELAY                                                               | 80  |

| EQUATION 5-4: RECURRENCE RESPONSE TIME                                                    | 81  |

| EQUATION 5-5: RESPONSE TIME                                                               | 83  |

| EQUATION 5-6: RESPONSE TIME (INCLUDING JITTER)                                            | 83  |

| EQUATION 5-7: COMMUNICATION TIME                                                          | 83  |

| EQUATION 5-8: BLOCKING DELAY                                                              | 84  |

| EQUATION 5-9: QUEUING DELAY                                                               | 84  |

| EQUATION 5-10: REOCCURRENCE QUEUING DELAY                                                 | 84  |

| EQUATION 5-11: CONVERGENCE                                                                | 84  |

| EQUATION 5-12: RESPONSE TIME                                                              | 84  |

| EQUATION 5-13: RECURRENCE RESPONSE                                                        | 85  |

| EQUATION 5-14: UPDATED RESPONSE TIME                                                      | 85  |

| EQUATION 5-15: WORSE CASE DELAY                                                           | 85  |

| EQUATION 5-16: UPDATED WCRT                                                               | 85  |

| EQUATION 5-17: UPDATED DELAY                                                              | 86  |

| EQUATION 5-18: TRANSMISSION TIME                                                          | 86  |

| EQUATION 5-19: SIMPLIFIED TRANSMISSION TIME                                               | 86  |

| EQUATION 6-1: USED MESSAGE SIZE OF NODE /                                                 | 103 |

| EQUATION 6-2: MAXIMUM MESSAGE SIZE OF NODE I                                              | 103 |

| EQUATION 6-3: DATA ELEMENT OPTIMUM PERIOD                                                 | 104 |

| EQUATION 6-4: OVERALL FITNESS                                                             | 104 |

| EQUATION 6-5: SLOT DURATION                                                               | 105 |

| EQUATION 6-6: SLOT REUSE                                                                  | 106 |

| EQUATION 6-7: M <sub>NEW</sub> TRANSMISSION SLOT PORTION WITHIN PERIOD(M <sub>NEW</sub> ) | 106 |

| EQUATION 6-8: DYN WORSE CASE RESPONSE TIME                                                | 109 |

| EQUATION 6-9: WORSE CASE DELAY $\Delta_M$                                                 | 110 |

| EQUATION 6-10: COMMUNICATION TIME                                                         | 110 |

| EQUATION 9-1: CAN MESSAGE SET                                                             | 132 |

| EQUATION 9-2: MESSAGE COMPONENTS                                                          | 132 |

| EQUATION 9-3: TASK GRAPH EXECUTION TIME                                                   | 132 |

| EQUATION 9-4: INTERMEDIATE TASK SCHEDULING                                                | 133 |

| EQUATION 9-5: TOTAL AVAILABLE SLACK                                                       | 133 |

# **Table of Equations**

| EQUATION 9-6: SLACK PER TASK                                  | 133 |

|---------------------------------------------------------------|-----|

| EQUATION 9-7: PARAMETER VALIDATION CHECK                      | 134 |

| EQUATION 9-8: TRANSMISSION DEADLINE                           | 134 |

| EQUATION 9-9: TRANSMISSION DELAY                              | 134 |

| EQUATION 9-10: FLEXRAY FRAME SIZE                             | 135 |

| EQUATION 9-11: FRAMES PER APPLICATION CYCLE (ST DATA)         | 135 |

| EQUATION 9-12: TOTAL REQUIRED BYTES                           | 136 |

| EQUATION 9-13: SLOT DURATION                                  | 138 |

| EQUATION 9-14: DISCRETISED SLOT DELAY                         | 138 |

| EQUATION 9-15: PERIODICITY AND DISTANCE CONSTRAINT VALIDATION | 140 |

| EQUATION 9-16: TOTAL DYN COMMUNICATION TIME                   | 141 |

| EQUATION 9-17: MINIMUM NUMBER OF REQUIRED DYN SLOTS           | 141 |

| EQUATION 9-18: SLOT QUANTITY VERIFICATION                     | 141 |

| EQUATION 9-19: DYNAMIC WORST CASE RESPONSE TIME               | 142 |

| EQUATION 9-20: COMMUNICATION TIME                             | 142 |

| EQUATION 9-21: ∆ <sub>M</sub> DELAY                           | 142 |

| EQUATION 9-22: NUMBER OF UNUSED MINISLOTS                     | 143 |

| EQUATION 9-23: W <sub>M</sub> (T) DELAY                       | 143 |

| EQUATION 12-1: TASK RESPONSE TIME                             | 187 |

| EQUATION 12-2: MESSAGE TRANSMISSION/COMMUNICATION TIME        | 187 |

| EQUATION 12-3: REVISED TOTAL FLEXRAY DATA                     | 194 |

| EQUATION 12-4: RESPONSE TIME ANALYSIS EQUATION                | 198 |

| EQUATION 12-5: TOTAL DYN COMMUNICATION TIME                   | 198 |

| EQUATION 12-6: Δ <sub>M</sub> DELAY                           | 199 |

| EQUATION 12-7: W <sub>M</sub> DELAY                           | 199 |

| EQUATION 12-8: RESPONSE TIME ANALYSIS EQUATION                | 209 |

| EQUATION 12-9: Δ <sub>M</sub> DELAY                           | 210 |

| FOLIATION 12-10: W., DELAY                                    | 210 |

# <u>Section I - Thesis</u> <u>Overview</u>

# 1 Thesis Overview:

#### 1.1 Problem Specification

The aim of this research is to develop a framework to migrate an application from CAN, an event driven network protocol, used principally in automotive applications to FlexRay, a time-triggered protocol. Within the automotive industry the predominant network has been CAN (Controller Area Network) and this is discussed in greater detail in Chapter 3. In the past eight to ten years it has been realised by automobile manufacturers that the CAN protocol will not be sufficient for future application requirements (Thomas Noltey, 2005). This is the main reason behind FlexRay's development. The FlexRay protocol is not intended necessarily to replace CAN. Through being able to operate a single protocol for an application this can reduce the complexity associated with operating multiple protocols via gateway/s. Consideration of various aspects of each protocol are to be take into account such as cost, knowledge of all protocols and the time required to implement these protocols are some examples of some of the possible issues encountered.

As consumers expect higher luxury levels in automobiles, this increases the loads on the current network protocols (Schedl, 2007). This, combined with the ever increasing amount of safety applications being developed, has resulted in predictions by Dr Anton Schedl at the Vector FlexRay Symposium 2007 amongst others, that current network protocols will not be able to cope with this demand in the near future (Schedl, 2007). In 2000 the FlexRay consortium was founded by automobile manufacturers BMW, Daimler Chrysler and semiconductor manufacturers Motorola semiconductors products sector (now Freescale semiconductors) and Philips semiconductors. Other leading companies in the automotive industry soon joined. It is anticipated that

FlexRay will replace CAN (as the de-facto automobile network) for critical and safety applications.

While FlexRay is anticipated as the solution to safety critical high speed applications, it is also anticipated that CAN technology will continue to be used in less critical applications. A migration from the CAN network to the FlexRay network would be required where CAN has reached maximum capacity or new features are added to an application that requires some of the features provided for on the FlexRay network. This research aims to provide a framework that will allow applications that have previously operated on the CAN network, to successfully operate on the FlexRay network.

#### 1.2 Specified Solution

One solution is to develop a framework to migrate from the CAN network to the FlexRay network. To achieve a successful migration a minimum requirement is that the minimum timing parameters in the CAN network are at least achieved or exceeded in the FlexRay network. This requires a detailed understanding of both network technologies, but specifically the FlexRay network as it is more complex.

# 1.3 Research Questions

#### Question 1:

What are the benefits of using the migration framework versus the use of a gateway?

#### Question 2:

What migration techniques used in other or similar protocols are applicable in this research?

#### Question 3:

What parameters are required in relation to the application and network protocol, for migration to be undertaken?

#### 1.4 Document Layout

The thesis is arranged as follows;

#### > Section I : Thesis Overview

This section, Thesis Overview presents the problem specification and the research questions.

#### > Section II : Literature Review

The Literature Review section discusses the background of automotive networks before presenting the CAN and FlexRay protocols in depth. An embedded system overview is discussed before the section concludes with a review of migration procedures carried out by other authors.

#### > Section III : Framework Development

This section, Framework Development, presents the requirements and methodology for undertaking this migration procedure.

# > Section IV : Testing & Results

Section IV, Testing & Results, presents the system model and the actual migration framework. The section proceeds with the abstract and experimental implementations of the generic model and the ACC (Adaptive Cruise Control) reference model and the Verification of Time-Triggered properties. The section concludes with a presentation of findings and a discussion of results.

#### > Section V : Conclusion

Section V contains the conclusion, and any potential future work that would improve this research.

#### > Section VI : Appendices

Section VI concludes the thesis with the appendices.

# Thesis Overview

#### 1.4.1 References

THOMAS NOLTEY, H. H., LUCIA LO BELLO (2005) Automotive Communications - Past, Current and Future

Schedl D A,2007, Goals and Architecture for FlexRay at BMW, 1st Vector FlexRay Symposium, Stuttgart, Germany.

# <u>Section II - Literature</u> <u>Review</u>

# 2 <u>Automotive Networks Review:</u>

#### 2.1 Introduction

This chapter contains a general assessment of what a computer network is, and reviews common network topologies. The TCP/IP and OSI reference model layers are presented due to their use in the transportation of data packets. This leads onto a history of automotive networks discussing various classes of automotive protocols. The Electronic Control Unit (ECU) is presented due to its core use in the development and implementation of networks in the automotive industry. Finally automotive protocols are discussed at event-triggered and time-triggered level and a direct comparison is made between the natures of both protocols.

#### 2.2 Computer Networks

"A network is a series of points or nodes interconnected by communication paths" (Harbeck, 2006)

The Internet is the most common data network that people come into contact with on a daily basis. The Internet evolved from a small academic research project involving a few dozen sites to become a vast worldwide system of interconnected networks providing various functions and services. The first computer networks were timesharing networks that used mainframes and attached terminals (Teare, 1999). Timesharing is the concept of multiple users getting access to the processor during the processors 'idle' time.

By networking remote locations to these 'powerful' computers (time-sharing) the required tasks could be completed more economically. Currently an entire industry provides networking technologies and services.

# Automotive Networks Review

#### 2.3 Network Function

A network consists of two or more devices interconnected as illustrated in Figure 2-1. One of the earliest network types was built to allow several computers to share a single printer.

A network's function is the transportation of data (e.g. data from a computer to a printer). Networking can be complex because there are so many different technologies available that can be used to connect two or more networks together (Comer, 2001). As data networks were developing during the 1970s and the 1980s the automotive industry was also starting to realise the advantages of implementing networks in automobiles. Originally, automobiles had relatively small quantities of electric and electronic components, usually in the form of closed loop circuits. For example, one of the earliest applications was the control and operation of lights. Additional features such as windscreen wipers and engine management systems increased the complexity and volume of wiring in the wiring harness. This led to the development of the bus structure in the 1980s. The de-facto bus structure in the automotive industry became the Controller Area Network (CAN). The structures of conventional data networks and automotive networks have some similarities. In the following section the features of both network types are discussed at network level in relation to the following; topology, architecture and protocols.

#### 2.4 Network Topologies

The term 'Topology' refers to the layout of the interconnecting devices on a network. There are two 'types' of topologies; the physical topology which describes the cable, node, and connector arrangements, and there is the logical topology which describes the arrangement of devices on a network (Steinke, 2000). The following description deals with physical topologies.

The main physical topologies are Bus, Star and Ring. The names are given in relation to the general shape of each network. The type of topology used depends on the configuration requirements of the system.

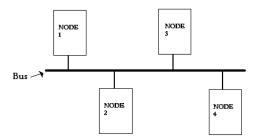

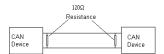

#### 2.4.1 Bus Topology

The Bus Topology (shown in Figure 2-2) can consist of a common medium, such as co-axial cable (10 base-2 (thin net) or 10 base-5 (thick net)) or un/shielded twisted pair (Institute, 2002).

Figure 2-2: Bus topology

All the other nodes on the network can be directly connected off this. Because all nodes share a common bus they can also share communication. The beginning and end of the bus are terminated to prevent signal reflecting back down the cable. If the central bus fails (e.g. the cable is cut) nodes at either side of the break can cease to function correctly, if they are required to communicate with each other. Using the CAN protocol information travels along the central bus and whichever node requests the

# Automotive Networks Review

information matches the message ID and then it can extract the information from the bus. If the message ID does not match the node ID the node does not gain access to that message. If a single node is removed from the network it does not affect the rest of the system.

# 2.4.2 Star Topology

The Star Topology is based on the principle of a centralised host through which all other nodes communicate (Figure 2-3). If one node wants to communicate with another node it is required to send the data through the central processor and then distribute it to the desired node. If the central processor node fails, subsequently communication is halted.

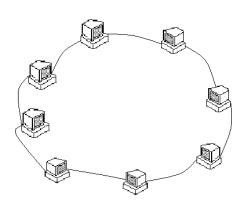

### 2.4.3 Ring Topology

The Ring Topology or Ring Network consists of each node being connected to-two other nodes to form a ring as illustrated in Figure 2-4. If one node sends data to a node that is not directly connected, the data has to go through all the other nodes in its path. The data can travel two paths (left or right) to get to its destination node.

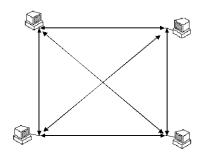

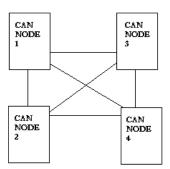

#### 2.4.4 Mesh Topology

In a fully connected Mesh Topology (as illustrated in Figure 2-5) every node is directly connected to all other nodes on the network. This makes it possible for all nodes to send data at the same time. This also allows for redundancy to be incorporated into any system using a mesh topology configuration. A message can take an alternative route if one route is corrupted or blocked. Due to the amount of wiring required this is considered a costly approach.

Figure 2-5: Mesh Topology

# **Automotive Networks Review**

#### 2.4.5 Hybrid Topology

These three topology types can be combined to make Hybrid Topologies such as a Tree Topology where there is a central bus and there is a ring and/or star topologies branching off.

#### 2.5 LAN (Local Area Network) & WAN (Wide Area Network)

Networks can generally be categorised in one of two fundamental groups; LAN (Local Area Network) and WAN (Wide Area Network). These incorporate some features from the OSI (Open Systems Interconnect) model which is discussed in detail in section 2.9.

#### 2.5.1 LAN

LANs connect as few as two devices together or as many as a few thousand. The interconnection between the devices can be via cable or wireless means. LANs usually connect devices that are in relative close proximity to each other such as a workstation and a printer in the same building. In a LAN, a server can contain data applications and services that other devices are allowed access. Ethernet is a technology that is widely associated with LANs. Ethernet LAN primarily deals with the physical and data-link layers (Teare, 1999). The MAC layer on a LAN uses a method called Carrier Senses Multiple Access/Collision Detection (CSMA/CD) for dealing with contention on the network. A device using CSMA/CD, listens on the network when it has data to be transmitted and, if no other device is using the network it transmits. After transmission it listens to see if a collision has occurred. If a collision has occurred each message is re-transmitted after a random length of time. If a number of other devices are using the network, performance degrades due to the increased number of collisions. Introducing switches on a network sub-divides the network into smaller collision domains resulting in less contention and improved performance.

# Automotive Networks Review

#### 2.5.2 WAN

WANs are used to connect multiple LANs over a larger area. A WAN uses dedicated or switched connections to link computers in geographically remote locations that are too widely dispersed to be directly linked to the LAN (Parnell, 1997). They can be connected via public telecommunications system or private communications. The Internet is an example of a public communications system.

#### 2.6 Communication Protocol

A communication protocol is a set of rules or standards that enables communications or data transfer between two end-points (SearchNetworking.com, 2007). A protocol enables communication between a host and a remote host as long as the communication takes place on the same level. If the rules are not kept then communication cannot occur. The TCP/IP reference model is illustrated in figure 2-6 but is not presented in detail as it is not covered in the scope of this research.

| Application    |  |

|----------------|--|

| Transport      |  |

| Internet       |  |

| Network Access |  |

#### 2.7 Automotive Networks History

As data networks began evolving, the automotive industry was beginning to add more electronic components and features to automobiles, such as air conditioning and electric windows. While data networks were developed to improve quality of service and increase data transfer rates, the automotive industries initial motivation would have been fundamentally financial. This has changed in recent years as the number of safety critical applications increases and consumers demand more comfort applications such as climate control. The introduction of a networked bus structure in automobiles has lead to a reduction in the size of wiring harnesses. Reducing the size of a wiring harness also yielded a reduction in the weight of the automobile and in turn this would improve fuel efficiency.

While initially introducing networks in cars reduced weight, this also lead to other safety/non-safety applications being developed, this increased weight and power consumption. The availability of integrated circuits in the 1960s and the 1970s allowed further development of automotive electronics and the development of the electronic control unit (ECU). The use of the ECU allowed engine management parameters to be varied depending on external conditions like engine load and air temperature. At the time, the main factor pushing automotive electronics development was exhaust emissions regulations. Mechanical methods alone could not provide the means to meet these new requirements while maintaining performance and efficiency (Fischerkeller, 2007). It was then realised that the microcomputer adapted for automotive use could address the requirements for emission controls while maintaining performance for the driving enthusiast. The microcomputer could handle data from the spark timing with variations in the load speed, inputs from sensors providing data on crankshaft position, coolant temperature etc (Jurgen, 1999). Increased development of integrated circuits allowed car manufacturers to eliminate passive components. Then with the development of microprocessor, electronic engine

# Automotive Networks Review

controls, anti-lock braking systems and trip computer revolutionised automobile electronics (Buchholz, 2006).

Originally, as automobile manufactures started to develop more electronic based applications for cars, there was no link between the electronics industry and the automotive industry. The automotive industry wanted the technology to be as economical as possible, but within the electronics industry all new technologies are initially expensive (due to research and development costs) and then become more cost effective due to improvements in production methods, product life cycles and widespread adaption.

It is no coincidence that during the 1980s the seminal breakthrough in automotive network development was facilitated by the production of more powerful ICs (Integrated Circuits). The CAN protocol was also developed during this period and by the early 1990s had become the de-facto standard in the automotive industry. There have been other variants of this protocol such as TTCAN, CANOpen, DeviceNet, CAN Kingdom and J1939. Proprietary variants such as J1850 PWM, J1850 VPM and ISO 9141-2 were developed individually by manufacturers but these are not included in the scope of this research. There are also three other primary automotive protocols. Local Interconnect Network (LIN) was developed as a low cost, lower speed alternative to CAN for use primarily in non-critical body control unit (BCU) functions. The Media Oriented System Transport (MOST) protocol was developed with high bandwidth infotainment systems specifically in mind. The FlexRay protocol was developed for use in safety critical applications.

#### 2.8 Automotive Networks Description

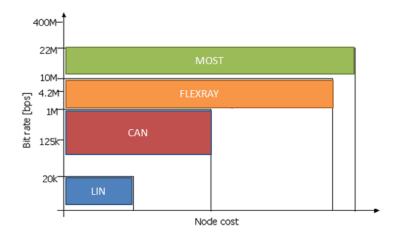

Automotive networks can be classified by their protocols. There are four main protocols CAN, LIN, FlexRay and MOST. Each protocol is selected for its ability to meet the system requirements while keeping the implementation and build costs as low as possible. The relative cost per data rate is illustrated in Figure 2-8.

A general rule of thumb is that the fastest networks tend to be the most expensive as is illustrated by Figure 2-8. LIN operates at speeds with a maximum data rate of 20 Kbit/s and is typically used in applications that require the driver to initiate operation. In critical applications that occur rapidly or do not require the driver to initiate operation the faster networks such as CAN and FlexRay with speeds of up to 10Mbit/s (1Mbit/s for CAN) are used even though they are more expensive to implement than LIN. In 1994 the Society of Automotive Engineers (SAE) defined the classification of four classes of networks; Class A, Class B, Class C and D.

- Class A: Data rates 10 kbits/ or lower

- Class B: Data rates from 10 to 125 kbits/s

- Class C: Data rates from 125 kbits/s to 1 Mbit/s

- Class D: Data rates over 1 Mbit/s

Class A is used in the body electronics of the car and an example is LIN as mentioned above. Class B is used to share information between ECUs to reduce the number of sensors required. A low speed CAN network would fall into this category. A class C network would be utilised by a real-time high-speed communications system i.e.

powertrain or chassis applications using high speed CAN. And finally the class D network is used by MOST and FlexRay in applications that require predictability and fault tolerance (NICOLAS NAVET, 2005).

While the protocol parameters change from protocol to protocol a basic network structure can be summarised in Figure 2-9. CAN (Controller Area Network) is the defacto network standard in the automotive industry. CAN operates on a peer-to-peer basis i.e. no master or slave, a message is transmitted and the node that requires the data gains access to the data and processes it.

Figure 2-8: Basic Network Configuration

In Figure 2-10 we see an illustration of a network configuration where each node is directly connected to every other node on the network (point-to-point). Figure 2-5 (mesh topology) is also an example of this as is previously explained. For a simple four-node system there is not much system complexity, but modern high to medium end automobiles have over 70 interconnected ECUs therefore dramatically increasing system complexity (A. Albert1, 2005). Networking eliminates redundant wiring because a sensor only has to be wired to the nearest controller and the controller will transmit the information over the network (Jared Busen, 2006).

Networking improves many aspects within the automotive industry such as design flexibility, diagnostics and reduced wiring/weigh/cost (Philip Koopman, 1998). Design flexibility is improved because designers just have to design as far as the controller and the network takes the information to the required controller in a different part of the automobile. Having one central access point on the network and connecting this into the diagnostics tool enables error messages on the bus to be read and analysed. This enables problems to be located quicker than having to test each functional area individually.

Networking allows the provision for scalability within a system. This allows a system to grow as more applications are added. A system can only grow if in the initial design stage provision is made for possible expansion or increased data through put at a later stage.

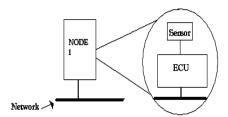

### 2.8.1 Generic Node Composition

Examining the components of a typical automotive network node reveals a general outline similar to that in Figure 2-11. Here a sensor provides input data to an Electronic Control Unit (ECU). The sensors data is processed in the ECU and transmitted across

the network so that any required actions will be taken if necessary. For output data we could have an actuator in place of the sensor.

Figure 2-10: A Basic Node Comprising of a Sensor and ECU

Before the introduction of ECUs into engine management systems the amount of fuel in a cylinder, quantity of air mixed in and the ignition time of the spark plugs were all parameters set by the designer at design time. By introducing ECUs this enabled these parameters to be mapped depending on varying engine load values, quality of air mixture etc. By having optimum operating conditions the car can achieve its best performance as efficiently as possible. With greater emphasis on reducing carbon emissions, it is with the aid of an ECU that these regulations can be met. The ECU receives data from the sensor and uses data tables and calculations to make adjustments to the actuating devices (Jurgen, 1999). The ECU can also help to perform system diagnosis whenever an error occurs.

### 2.9 ECU

The electronic control unit (ECU) in an automobile has three main functions;

- Perform decision-making capabilities (e.g. adjust intake values)

- Perform arithmetic calculations

- Store data

- Read inputs from sensors

- Perform Actuations based on decisions

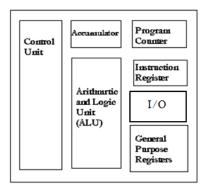

The ECU is based around the microprocessor because it can perform the three basic requirements as mentioned above. Modern automobiles need processing capabilities of computers and computers are based around microprocessors. The microprocessor acts as a CPU (Central Processing Unit) for a computer. Early microprocessors processed up to eight bits at a time but nowadays microprocessors are available in 16-bit and 32-bit format, which enables higher processing speeds.

The CPU works in a sequential manner and a clock, usually a crystal clock, controls the timing. This enables frequencies of several megahertz giving higher processor speeds and greater accuracy for clock samples. When an instruction is received and needs temporary storage in the CPU it is stored in the memory registers. Within the registers each word received is stored in memory.

Figure 2-12 illustrates a microprocessor with associated registers. It also illustrates the program counter that keeps track of where any instructions are stored and what instructions the CPU requires running. The ALU (Arithmetic Logic Unit) performs the arithmetic calculations in binary. Any data that is being processed by the ALU is stored in the accumulator until the calculation is finished. The control unit directs movement of data in the computer. What enables a microprocessor to carry out instructions in

the desired manner are the instructions it receives, these instructions would usually be conveyed via software through a program.

A basic computer can consist of the following elements; a microprocessor, extra memory, inputs and outputs. Data is stored at a specific address is memory and, when the processor requires data, fetches it from that address.

When storing data in memory the type of memory used is influenced by the tasks function. Source code does not change and therefore would be stored in ROM (Read Only Memory). If the same task was performed repeatedly without change in the process then ROM type of memory can be selected, an example of this would be on a fuel management system that uses fixed data. If the data is only required for a temporary period then RAM (Random Access Memory) can be used. Once the power is disconnected from this type of memory the data is lost. An example of this would be a trip computer in a automobile (also called run-time data) (Hillier, 1996). Non-volatile RAM (NVRAM) is also used in instances where stored data is not to be erased. The primary area where NVRAM is used is in data recording such as in the odometer.

A bus interconnects the components of the microprocessor; these buses are named in relation to the data they carry such as the address bus, data bus and control bus. For an automotive based computer the inputs and outputs would typically be sensors, transducers and actuators.

Current practice in the automotive industry is that the physical network bus interconnecting between nodes is a cable. Connectors attach the cable to the hardware. The <u>protocol is a contributing factor when</u> cable specifications are set.

### 2.10 Automotive Network Protocols

As discussed in the previous section one reason for introducing networks into modern automobiles was due to the increased levels of new features and applications in automobiles. Design engineers decide what protocol is run on the network. Some

considerations that have to be taken into account when deciding what protocol shall be used are;

- Is the application critical?

- What speeds are required for the application?

- What costs are associated with each protocol?

- Is the technology readily available to develop the application with the chosen protocol?

The answer to these questions will often decide the protocol chosen, whether it is an event-triggered (ET) or time-triggered (TT) system.

### 2.10.1 Event-Triggered Protocols

In an event-triggered (ET) system, traffic gets put onto the network after an event has occurred such as the driver pressing the brakes. This is asynchronous transfer because there is no predetermined time at which these events will occur. Because any event can occur at any time in any order, the network has to have a developed system that will avoid collisions if two messages on two separate nodes try to gain access to the network at the same time. This is achieved by tagging each message with a priority level. The message with the highest priority will be granted access to the bus once it is free. This is an efficient use of bandwidth due to the fact that only messages that need to be transmitted will be looking for access to the network (NICOLAS NAVET, 2005). An event-triggered communication controller does not need a dispatching table because the transmission of a message is triggered by a send command from the host (Kopetz, 2000).

#### 2.10.2 Time-Triggered Protocols

With the time-triggered (TT) protocol, transmission occurs at predefined points in time (Andrei Hagiescu, 2007). Activities can only occur with the progression of time and the activity is predefined. This requires the network to have a pre-defined schedule that assigns activities/tasks a section of the time (time slot) to perform the required action. Each task is made up of messages. If a message is not transmitted in its defined time slot it waits until its next time slot.

In Figure 2-13, a message is assigned slot two (S2) in which to transmit. If the message does not obtain access to the bus in slot (S2) its next assigned slot where it will get a chance to gain access to the bus is in slot seven (S7).

A time-triggered communication controller contains a dispatching table in its local memory that determines what point in time a particular message is transmitted or when that message is expected to be received (Kopetz, 2000). If a new node is added to the network all other nodes need to be updated due to a change in the schedule (if the new node was an unplanned addition). This can result in inefficient bandwidth usage as some messages might not need to transmit the whole time, but will need to be allocated slots by the system designer (Andrei Hagiescu, 2007).

### 2.10.3 Comparison of Event-Triggered and Time-Triggered Networks

ET systems have an advantage over TT systems when it comes to adding new nodes onto the network. With ET systems the new node can be added on where as in TT systems the new node has to be scheduled into the system at design time. This

involves the system designer re-organising the system schedule to accommodate the new IDs on the new node. As stated previously bandwidth efficiency is greater on ET systems because a message can be transmitted if bandwidth is available where as on a TT system a message can only transmit when it has been scheduled to do so even if there are no messages scheduled in the slots before it. TT systems can be fault tested to a higher degree because the designer has the schedule prior to execution. In ET systems run time testing is critical for catching potential faults due to the aperiodic nature of the protocol. Also in TT networks, since the application does not control the timings there is a common time base for all nodes which allows the communication controller to synchronise to the message schedule (Hartwich, 2007).

After considering these features the properties of each protocol can be examined. Only CAN and FlexRay are discussed as LIN and MOST were not encountered during this research.

### 2.11 Conclusion

In this chapter the concept of computer networks was introduced starting with the general principle and moving onto automotive systems. Differing network topologies and architectures were discussed before an example of the TCP/IP reference model is presented, whose protocol is used extensively in the Internet. The seven layers of the OSI reference model are explained as this reference model is used to compare layers of other protocols. A brief history about the reasons for using of networks within the automotive industry is presented along with an overview of a nodes hardware composition. Finally the chapter concludes with a discussion on TT and ET protocols and a comparison of strengths and weakness of the two.

This chapter presents the necessary background to understanding the purposes and requirements of networks within the automotive industry. By presenting data network models such as the OSI model this allows comparisons to be made when discussing automotive protocols in later chapters such as the comparison made in Chapter 3 between CAN and the OSI model. By presenting an overview of the various network

types (TT and ET) the limitations and advantages of each architecture type are revealed.

#### 2.12 References

A. Albert1 B P, F. Voetz1,2005, Simulation Environment for Investigating the Impacts of Time-Triggered Communication on a Distributed Vehicle Dynamics Control System, 1st International ECRTS Workshop on Real-Time and Control,

Andrei Hagiescu U D B, Samarjit Chakraborty, Prahladavaradan Sampath, P.Vignesh, V. Ganesan, S. Ramesh, 2007 Performance Analysis of FlexRay-based ECU Networks

Buchholz K, 2006, Electronics history lesson.

http://www.sae.org/automag/electronics/09-2002/

Casad J 2001 Teach Yourself TCP/IP in 24 Hours: Sams)

Comer D E 2001 Computer Networks and Internets: Prentice Hall)

Fischerkeller S R a R, 2007, Latest Trends In Automotive Electronic Systems - Highway Meets Off-Highway?

Harbeck R, 2006, Network,

http://searchnetworking.techtarget.com/sDefinition/0,sid7 gci212644,00.html [15/03/2008]

Hartwich F,2007, Implementation Concept for Bosch FlexRay Communication controller, 1st Vector FlexRay symposium, Stuttgart.

Hillier V A W 1996 Hilliers Fundamentals of Automotive Electronics: Stanley Thornes Ltd)

Institute N B R, 2002, INFORMATION COMMUNICATION TECHNOLOGY (ICT)

DEVELOPMENTS – ESTABLISHMENT OF THE FIRST SWITCH BASED LOCAL AREA

NETWORK AT NBRI (NBRI-LAN), [26/02/2008]

Jared Busen L E J a B K, 2006, How Automotive Networks are Configured, http://www.asashop.org/autoinc/jan2006/mech2.htm [10-Feburary-2008]

Jurgen R K 1999 Automotive Electronics Handbook: McGraw-Hill)

Kopetz H, 2000, A Comparison of CAN and TTP, Editor, Conference Name, Conference Location.

NICOLAS NAVET Y S, FRANÇOISE SIMONOT-LION, AND CÉDRIC WILWERT, 2005, Trends in Automotive Communication Systems, Editor, PROCEEDINGS OF THE IEEE,