### Firmware Deployment of Strong Encryption: An Investigation and Implementation

John Ronan

$12 \mathrm{th}~\mathrm{July}~2001$

### Waterford Institute of Technology Department of Physical and Quantitative Sciences

Firmware Deployment of Strong Encryption:

An Investigation and Implementation

$\begin{array}{c} {\rm A~thesis} \\ {\rm submitted~for~the} \\ {\rm Degree~of~Master~of~Science~to} \\ {\rm the~National~Council~of~Educational~Awards} \\ {\rm by} \end{array}$

John Ronan

To my parents, grandparents and Deirdre.

Acknowledgements: Eamonn de Leastar, Dr Willie Donnelly, Dr Martin Hayes, Michael O'Foghlu, Jimmy McGibney, Michael McCarthy, Kristian Walsh, and my colleagues in the Telecommunications Software Systems Group.

#### Abstract

Software encipherment and an equivalent firmware implementation is the general scope of this work. Current cryptographic implementations rely on software running under general purpose, often multi-user, operating systems alongside a horde of untrusted and possibly malicious applications. Additionally there are other threats to security, such as that posed by "crackers" or government agencies listening in to network traffic. This work addresses one method for minimising these risks.

A framework is presented for implementation of a cryptographic coprocessor, capable of securely performing encryption, decryption and key management. To achieve maximum performance and security the algorithm is instantiated in firmware. This achieves superior performance to pure software implementations.

This work also examines various issues related to the choice of algorithms out "in the wild" today, how they operate, and how they can be used for different purposes. It shows how a software algorithm can be brought into the hardware/firmware domain and deployed as effectively therein. The framework implemented retains all the functionality of the pure software solution while gaining significantly in performance. This approach is also significantly more secure, as a firmware implementation is not open to the standard security workarounds and breaches commonly applied to software solutions.

As part of the project a corresponding software implementation has been verified against the firmware equivalent, and an assessment made on the relative merits of both approaches with respect to speed, security, and ease of implementation.

### Contents

| 1 | Intr | oducti | on & Background                                          | 1  |

|---|------|--------|----------------------------------------------------------|----|

|   | 1.1  | Compu  | ıter Security                                            | 2  |

|   |      | 1.1.1  | Goals                                                    | 4  |

|   | 1.2  | Crypto | ography                                                  | 4  |

|   |      | 1.2.1  | A Brief History                                          | 4  |

|   |      | 1.2.2  | The Fundamental Idea of Cryptography                     | 5  |

|   |      |        | 1.2.2.1 The Single Transformation                        | 6  |

|   |      |        | 1.2.2.2 Many Transformations                             | 7  |

|   |      |        | 1.2.2.3 Weak and Strong Transformations                  | 7  |

|   |      |        | 1.2.2.4 Key-space                                        | 8  |

|   |      |        | 1.2.2.5 Digital Electronic Ciphering                     | 9  |

|   |      | 1.2.3  | What Cryptography $Can$ do $\ldots \ldots \ldots \ldots$ | 11 |

|   |      | 1.2.4  | What Cryptography Can Not do                             | 12 |

|   |      | 1.2.5  | Problems with Keys                                       | 13 |

|   |      | 1.2.6  | Strength                                                 | 14 |

|   |      | 1.2.7  | System Design and Strength                               | 14 |

|   |      | 1.2.8  | Cryptanalysis versus Subversion                          | 15 |

|   |      | 1.2.9  | Secret Ciphers                                           | 15 |

|   |      | 1.2.10 | Hardware vs Software Ciphers                             | 17 |

|   |      | 1.2.11 | Block & Stream Ciphers                                   | 18 |

|   |      | 1.2.12 | Public Key Ciphers                                       | 18 |

|   |      | 1.2.13 | Quantum Leap                                             | 19 |

|   |      | 1.2.14 | The Advanced Encryption Standard (AES) $\dots \dots$     | 19 |

|   | 1 2  | Thoric | Structuro                                                | 20 |

CONTENTS v

| 2 | Enc  | ryptio | n Algorithm                                                                                                                                                                            | 22      |

|---|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|   | 2.1  | Introd | uction                                                                                                                                                                                 | 23      |

|   | 2.2  | Algori | thm Selection                                                                                                                                                                          | 23      |

|   | 2.3  | 3way:  | The Basic Building Blocks                                                                                                                                                              | 25      |

|   |      | 2.3.1  | $\mu$                                                                                                                                                                                  | 26      |

|   |      | 2.3.2  | The Nonlinear substitution $\gamma$                                                                                                                                                    | 26      |

|   |      | 2.3.3  | The Linear Substitution $\theta$                                                                                                                                                       | 26      |

|   |      | 2.3.4  | $\pi_1$ and $\pi_2$                                                                                                                                                                    | 27      |

|   |      | 2.3.5  | The Structure of the Block Cipher                                                                                                                                                      | $^{27}$ |

|   | 2.4  | Cipher | Modes Explained                                                                                                                                                                        | 28      |

|   |      | 2.4.1  | ECB mode                                                                                                                                                                               | 28      |

|   |      | 2.4.2  | CBC mode                                                                                                                                                                               | 29      |

|   |      | 2.4.3  | CFB Mode                                                                                                                                                                               | 31      |

|   |      | 2.4.4  | OFB Mode                                                                                                                                                                               | 32      |

|   |      | 2.4.5  | Choosing a cipher mode                                                                                                                                                                 | 34      |

|   |      | 2.4.6  | Key Generation                                                                                                                                                                         | 34      |

|   | 2.5  | Refere | nce Code - A short tour                                                                                                                                                                | 35      |

|   |      | 2.5.1  | main                                                                                                                                                                                   | 37      |

|   |      | 2.5.2  | encrypt                                                                                                                                                                                | 37      |

|   |      | 2.5.3  | $rndcon\_gen \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                  | 38      |

|   |      | 2.5.4  | ${\rm rho} \ldots \ldots$                                                                                        | 38      |

|   |      | 2.5.5  | $theta\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots\dots$ | 39      |

|   |      | 2.5.6  | pi_1 & pi_2                                                                                                                                                                            | 39      |

|   |      | 2.5.7  | $mu \ \dots $                                                                    | 40      |

|   |      | 2.5.8  | gamma                                                                                                                                                                                  | 40      |

|   |      | 2.5.9  | $\operatorname{decrypt} \ \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                     | 42      |

|   |      | 2.5.10 | CBC Mode Implementation                                                                                                                                                                | 42      |

|   | 2.6  | Conclu | ısion                                                                                                                                                                                  | 42      |

| 3 | Firr | nware  |                                                                                                                                                                                        | 43      |

|   | 3.1  | Introd | uction                                                                                                                                                                                 | 44      |

|   |      | 3.1.1  | Definitions of Relevant Terminology                                                                                                                                                    | 44      |

|   |      | 3.1.2  | Evolution of Programmable Logic Devices                                                                                                                                                | 45      |

|   |      | 3.1.3  | Computer Aided Design (CAD) Flow for FPDs                                                                                                                                              | 46      |

|   |      | 3.1.4  | Commercially Available FPGAs                                                                                                                                                           | 47      |

|   | 3.2  | Altera | & MAX+PLUS II                                                                                                                                                                          | 49      |

|   |      | 3.2.1  | AHDL Design Language                                                                                                                                                                   | 50      |

|   |     | 3.2.2 Text Design File Sections             | 50 |

|---|-----|---------------------------------------------|----|

|   |     | 3.2.3 Firmware & Software: Differences      | 52 |

|   | 3.3 | 3way: The Basic Building Blocks             | 52 |

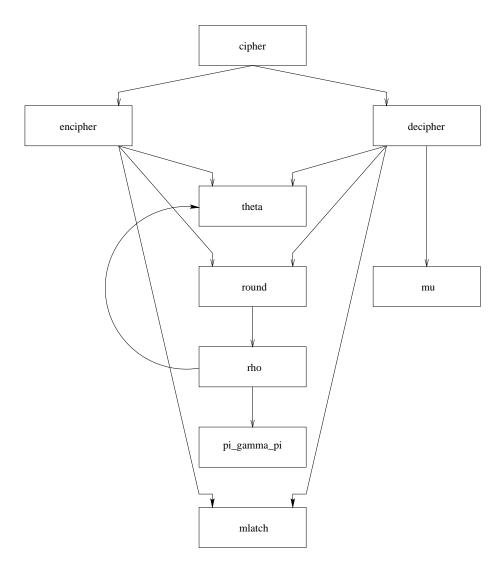

|   |     | 3.3.1 cipher                                | 53 |

|   |     | 3.3.2 encipher                              | 55 |

|   |     | 3.3.3 mlatch                                | 55 |

|   |     | 3.3.4 round                                 | 55 |

|   |     | 3.3.5 rho                                   | 56 |

|   |     | 3.3.6 pi_gamma_pi                           | 56 |

|   |     | 3.3.7 theta                                 | 56 |

|   |     | 3.3.8 decipher                              | 56 |

|   |     | 3.3.9 mu                                    | 57 |

|   | 3.4 | Conclusion                                  | 57 |

| 4 | Det | ployment                                    | 58 |

| - | 4.1 |                                             | 59 |

|   | 4.2 | _                                           | 59 |

|   | 4.3 |                                             | 62 |

|   | 0   |                                             | 64 |

|   | 4.4 |                                             | 68 |

|   |     | 4.4.1 PCI10K-PROD Board                     | 69 |

|   |     |                                             | 69 |

|   |     |                                             | 70 |

|   |     |                                             | 74 |

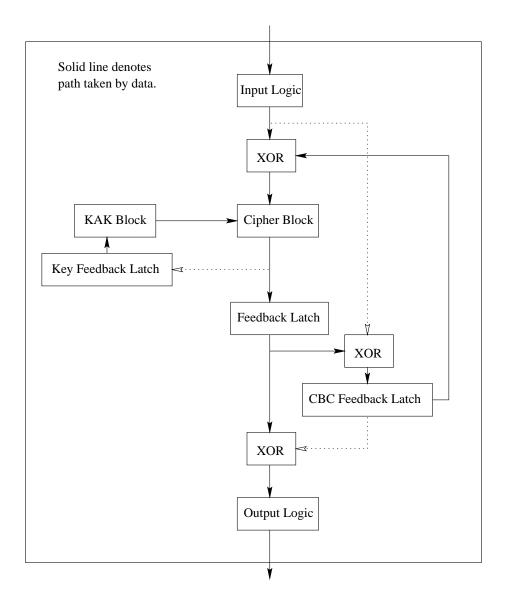

|   |     | 4.4.2.3 feedbacklogic                       | 74 |

|   |     | 4.4.2.4 cbcreset                            | 74 |

|   |     | 4.4.2.5 core                                | 74 |

|   |     | 4.4.2.6 controlncore                        | 74 |

|   |     | 4.4.2.7 crypto                              | 75 |

|   |     | 4.4.2.8 display_control.vhd                 | 75 |

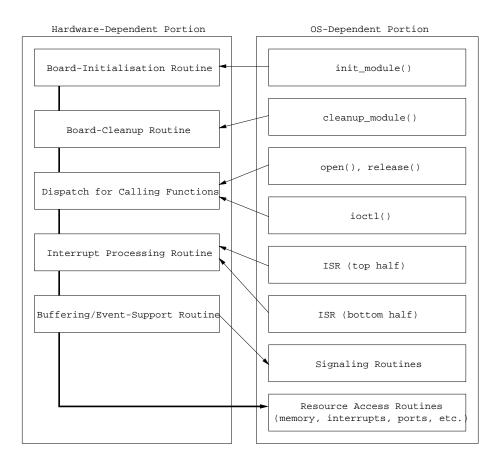

|   |     | 4.4.3 Device driver initialisation sequence | 75 |

|   | 4.5 | Conclusion                                  | 77 |

| 5 | Res | sults and Conclusions                       | 79 |

| ŭ | 5.1 | , <del></del>                               | 80 |

|   | 2   |                                             | 80 |

|   |     | 5.1.1.1 Comparison                          | 80 |

| CC | ONTE       | <i>NTS</i> vii                         |

|----|------------|----------------------------------------|

|    |            | 5.1.2 Alpha                            |

|    |            | 5.1.2.1 Comparison                     |

|    | 5.2        | Conclusions and Future Work            |

| A  | 3way       | y Reference Code 92                    |

| В  | Alte       | ra Text Design Files 96                |

|    | B.1        | Cipher                                 |

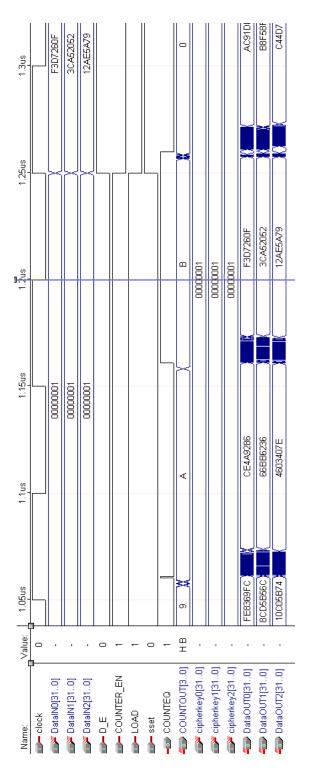

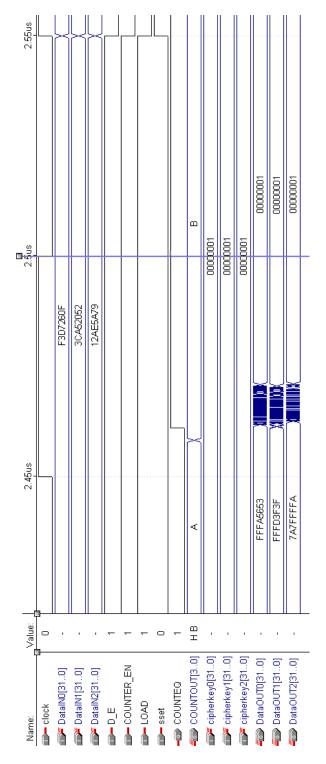

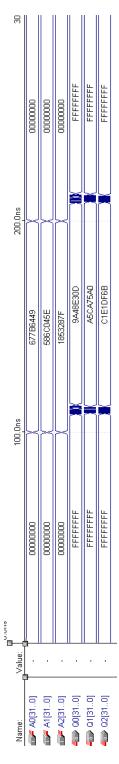

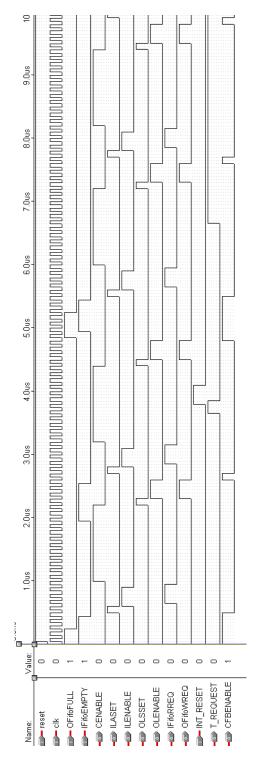

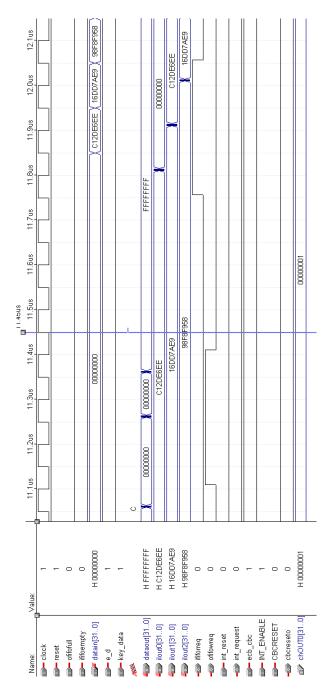

|    |            | B.1.1 Timing Diagrams, Cipher          |

|    | B.2        | encipher                               |

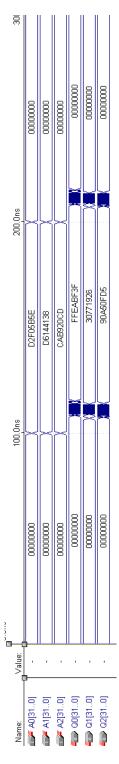

|    |            | B.2.1 Timing diagrams, encipher        |

|    | B.3        | mlatch                                 |

|    | <b>B.4</b> | round                                  |

|    | B.5        | rho                                    |

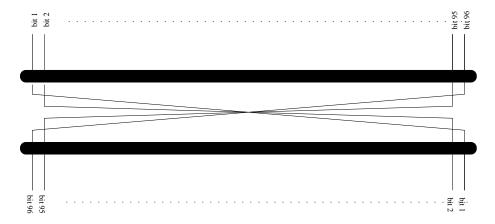

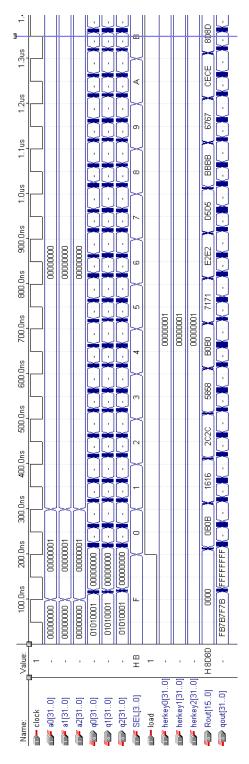

|    |            | B.5.1 Timing diagram, rho              |

|    | B.6        | pi_gamma_pi 108                        |

|    |            | B.6.1 Timing diagram, pi_gamma_pi      |

|    | B.7        | theta                                  |

|    |            | B.7.1 Timing diagram, theta            |

|    | B.8        | decipher                               |

|    |            | B.8.1 Timing diagram, decipher         |

|    | B.9        | mu                                     |

|    | B.10       | inputlogic                             |

|    | B.11       | key-authenthication-key                |

|    | B.12       | feedbacklogic                          |

|    | B.13       | outputlogic                            |

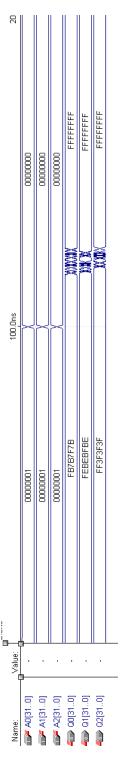

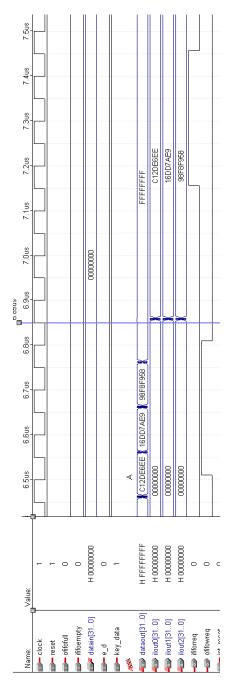

|    |            | B.13.1 Timing diagram, outputlogic 125 |

|    | B.14       | cbcreset                               |

|    | B.15       | core                                   |

|    | B.16       | controlncore                           |

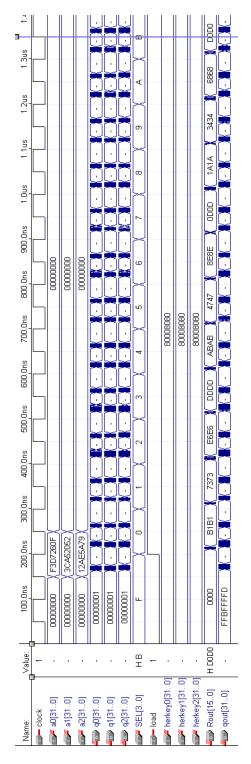

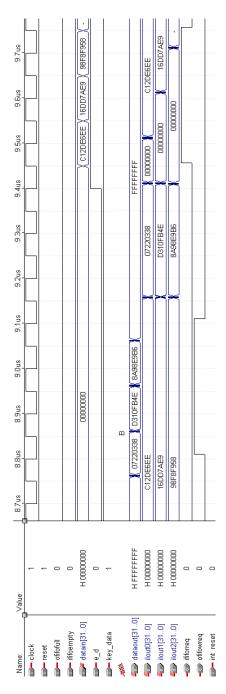

|    |            | B.16.1 Timing diagram, Controlncore    |

|    | B.17       | crypto                                 |

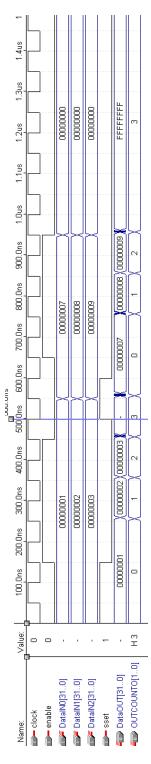

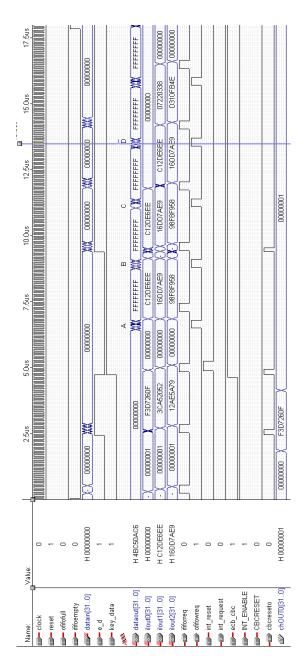

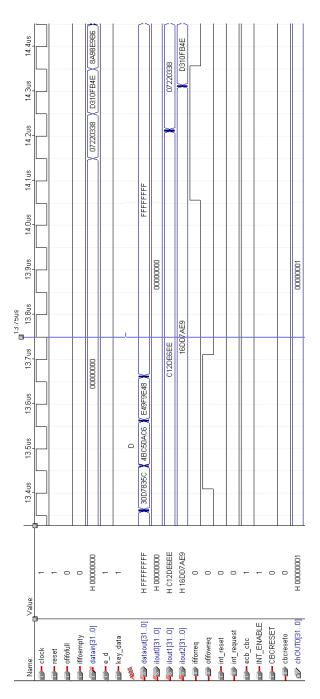

|    |            | B.17.1 Timing Diagrams, Crypto         |

|    | B.18       | display_ctrl.vhd                       |

| $\mathbf{C}$ | Dev  | ice Driver | •  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 144 |

|--------------|------|------------|----|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

|              | C.1  | 3way.h     |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 144 |

|              | C.2  | 3way.c     |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 144 |

|              | C.3  | common.h   |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 146 |

|              | C.4  | software.h |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 147 |

|              | C.5  | Software.c |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 147 |

|              | C.6  | driver.h . |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 153 |

|              | C.7  | driver.c . |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 154 |

|              | C.8  | hardware.l | 1  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 166 |

|              | C.9  | hardware.  | :. |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 168 |

|              | C.10 | mode.c     |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 178 |

|              | C.11 | Makefile . |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 185 |

|              | C.12 | testenc.sh |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 185 |

|              | C.13 | testdec.sh |    |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 186 |

# List of Figures

| 2.1 | Theta, bit shifter                                          | 27 |

|-----|-------------------------------------------------------------|----|

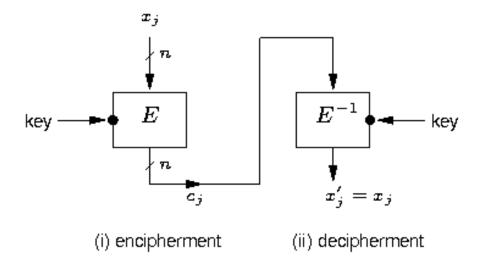

| 2.2 | ECB Mode                                                    | 29 |

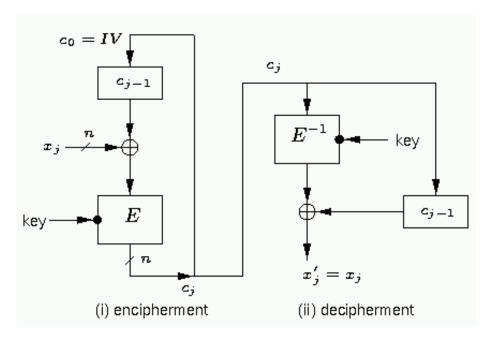

| 2.3 | CBC Mode                                                    | 30 |

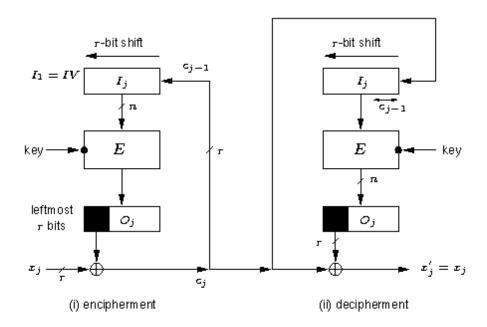

| 2.4 | CFB Mode                                                    | 31 |

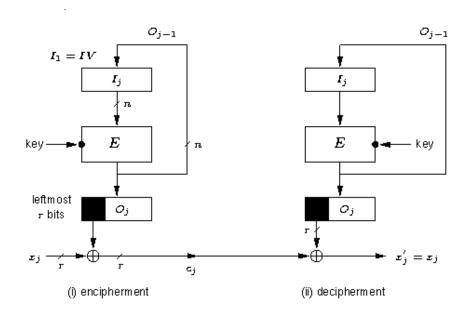

| 2.5 | OFB Mode                                                    | 33 |

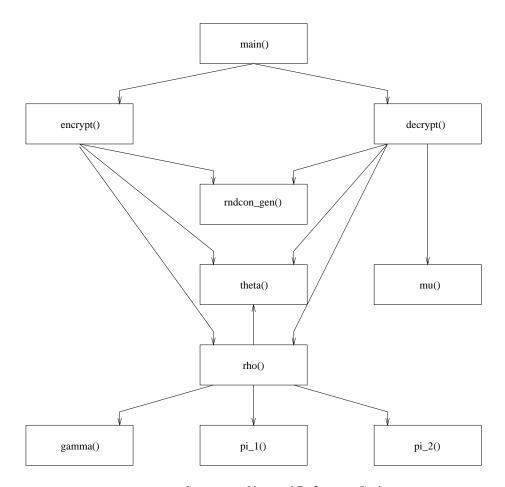

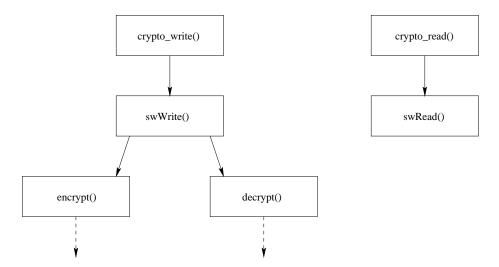

| 2.6 | Structure Chart of Reference Code                           | 36 |

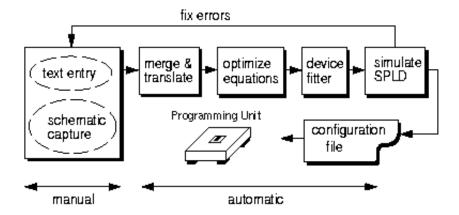

| 3.1 | CAD Design Flow for SPLDs[BR00]                             | 47 |

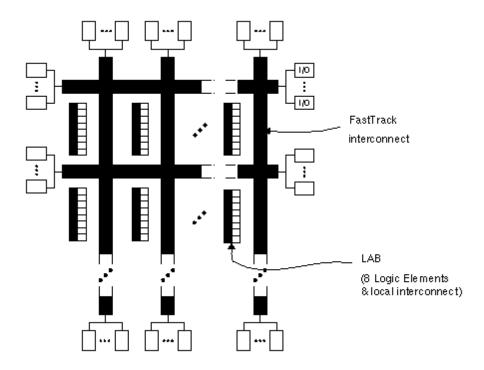

| 3.2 | Flex 10K Architecture                                       | 48 |

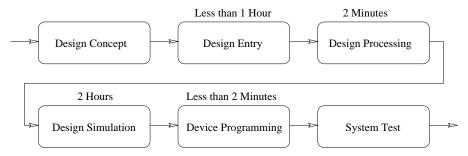

| 3.3 | Altera PLD development cycle using the Quartus & MAX+PLUS   |    |

|     | II Software                                                 | 49 |

| 3.4 | Firmware block diagram                                      | 54 |

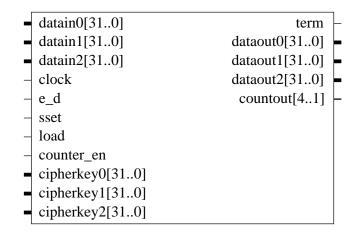

| 3.5 | Cipher                                                      | 55 |

| 3.6 | Firmware Mu                                                 | 57 |

| 4.1 | Structural diagram of pseudo device driver                  | 62 |

| 4.2 | Device Driver Architecture                                  | 63 |

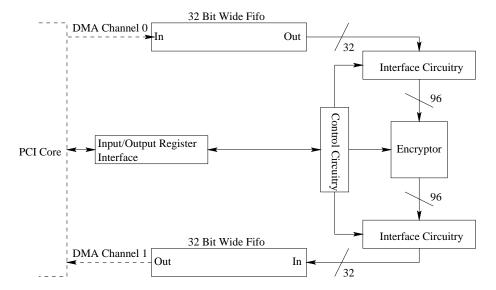

| 4.3 | PCI Core & Interface Circuitry                              | 70 |

| 4.4 | Flowchart of Session Key Decryption. (ECB Mode, $\S 2.4.1)$ | 71 |

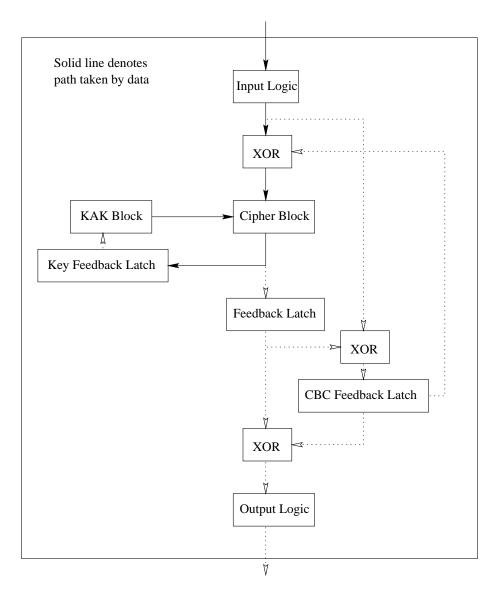

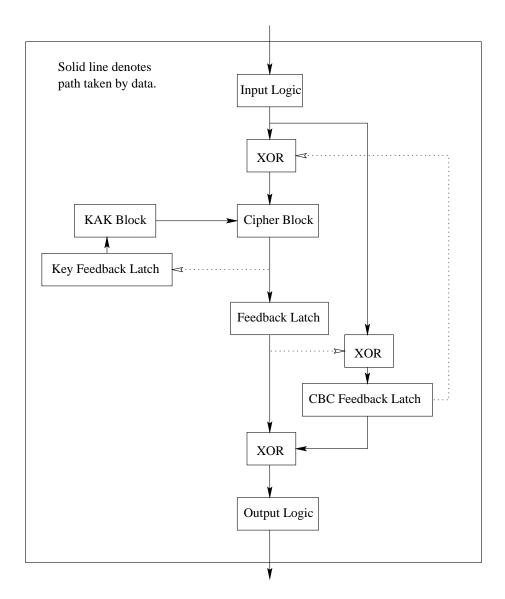

| 4.5 | Flowchart of CBC Mode (§2.4.2) Decryption                   | 72 |

| 4.6 | Flowchart of CBC Mode (§2.4.2) Encryption                   | 73 |

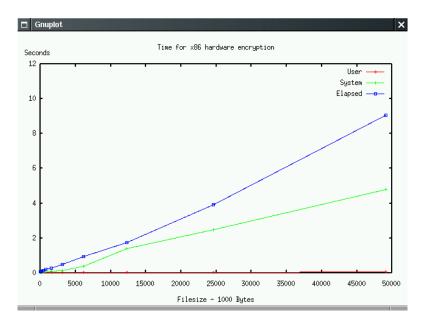

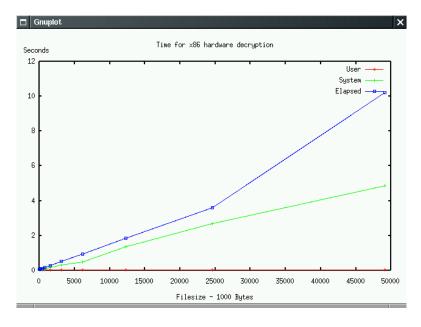

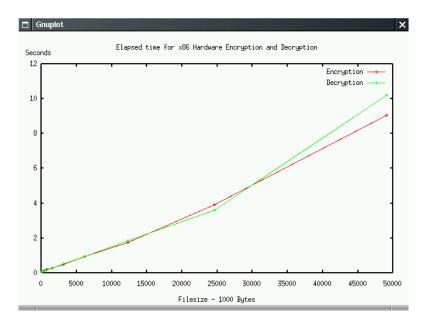

| 5.1 | Elapsed time for x86 hardware encryption                    | 81 |

| 5.2 | Elapsed time for x86 hardware decryption                    | 81 |

| 5.3 | Comparison of x86 hardware encryption vs decryption         | 82 |

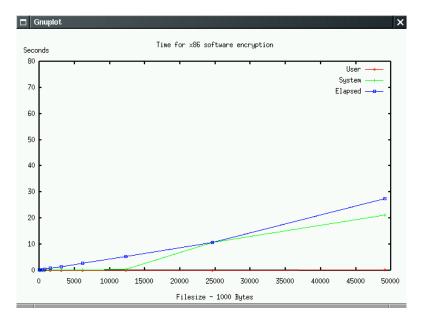

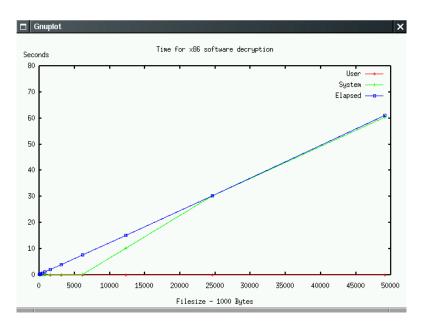

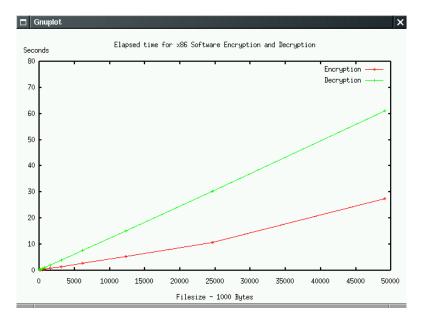

| 5.4 | Elapsed time for x86 software encryption                    | 82 |

| 5.5 | Elapsed time for x86 software decryption                    | 83 |

| 5.6 | Comparison of x86 software encryption vs decryption.        | 83 |

LIST OF FIGURES x

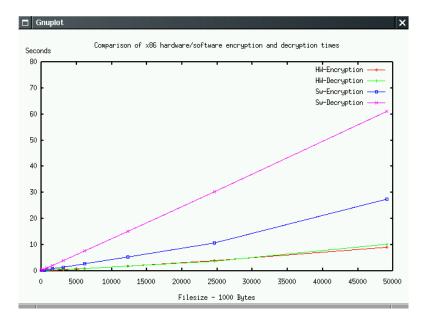

| Comparison of x86 software vs hardware implementation 8                                | 34                                         |

|----------------------------------------------------------------------------------------|--------------------------------------------|

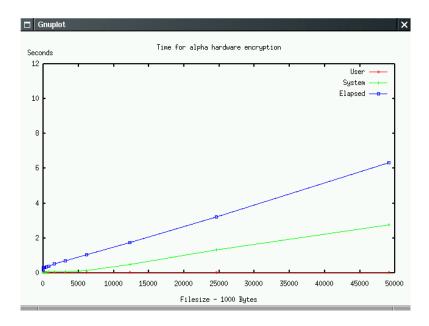

| Elapsed time for Alpha hardware encryption 8                                           | 35                                         |

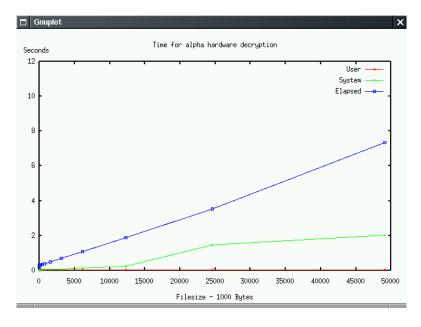

| Elapsed time for alpha hardware decryption 8                                           | 35                                         |

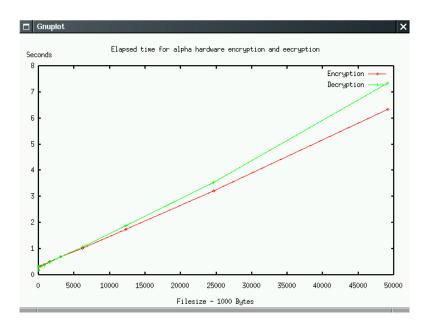

| Comparison of Alpha hardware encryption vs decryption 8                                | 86                                         |

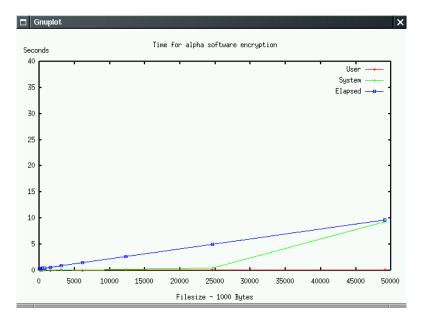

| Elapsed time for Alpha software encryption                                             | 86                                         |

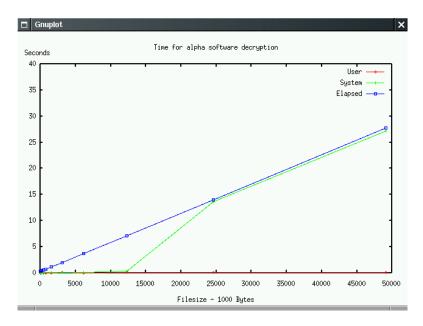

| Elapsed time for Alpha software decryption                                             | 37                                         |

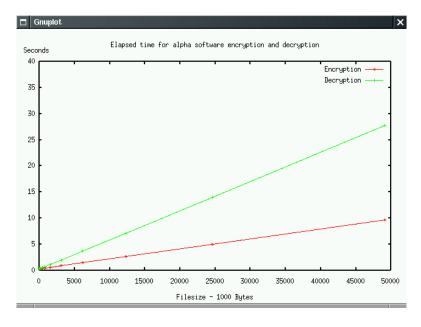

| Comparison of Alpha software encryption vs decryption 8                                | 37                                         |

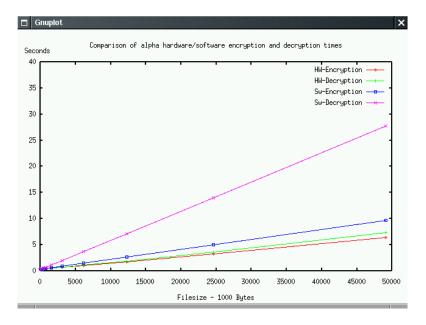

| Comparison of Alpha software vs hardware implementation $$ 8                           | 88                                         |

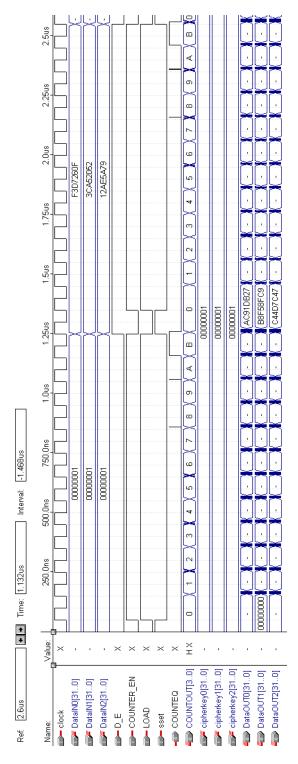

| Cipher, full test timing diagram                                                       | 9                                          |

| Cipher, end of encryption cycle, close up                                              | 0                                          |

| Cipher, end of decryption cycle, close up                                              | 1                                          |

| Encipher, full test timing diagram                                                     | 15                                         |

| Rho, full test timing diagram                                                          | 9                                          |

| $Pi\_gamma\_pi, full \ test \ timing \ diagram. \ . \ . \ . \ . \ . \ . \ . \ . \ . \$ | .3                                         |

| Theta, full test timing diagram                                                        | .7                                         |

| Decipher, full test timing diagram                                                     | 21                                         |

| Outputlogic, full test timing diagram, close up                                        | 26                                         |

| Control circuitry, full test timing diagram                                            | 34                                         |

| Crypto, full test timing diagram                                                       | 6                                          |

| Crypto, end of first encryption cycle, close up                                        | 37                                         |

| Crypto, end of second encryption cycle, close up                                       | 8                                          |

| Crypto, end of first decryption cycle, close up                                        | 39                                         |

| Crypto, end of second decryption cycle, close up                                       | ŀ0                                         |

|                                                                                        | Elapsed time for Alpha hardware encryption |

## List of Tables

| 1.1 | Key Classification                                           | 6  |

|-----|--------------------------------------------------------------|----|

| 1.2 | Average Time Estimates for a Hardware Brute -Force Attack in |    |

|     | 1995                                                         | 10 |

| 2.1 | Modes of Operation                                           | 34 |

# List of Algorithms

| 1  | 3way pseudo algorithm.[Sch96, p342]                                                                                                                    | 8 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2  | 3way, main()                                                                                                                                           | 7 |

| 3  | 3 way,  encrypt()  .  .  .  .  .  .  .  .  .                                                                                                           | 7 |

| 4  | $3$ way, $rndcon_gen()$                                                                                                                                | 8 |

| 5  | 3way, rho()                                                                                                                                            | 8 |

| 6  | 3way, theta()                                                                                                                                          | 9 |

| 7  | 3way, pi_1 & pi_2                                                                                                                                      | 9 |

| 8  | $3way,mu()\ldots\qquad \qquad $ | 0 |

| 9  | 3way, gamma()                                                                                                                                          | 1 |

| 10 | $3 way, \ decrypt() \ \dots \ \dots \ \dots \ \ 4$                                                                                                     | 1 |

| 11 | Kernel version of "Hello World" 6                                                                                                                      | 1 |

| 12 | Extract from driver.h, §C.6 6                                                                                                                          | 5 |

| 13 | Extract from driver.c, §C.7 6                                                                                                                          | 6 |

| 14 | Extract from driver.c, §C.7 6                                                                                                                          | 7 |

| 15 | Extract from driver.c, §C.7 6                                                                                                                          | 8 |

| 16 | Extract from hardware.c, §C.9                                                                                                                          | 6 |

| 17 | Extract from hardware.c, §C.9                                                                                                                          | 7 |

| 18 | Extract from hardware.c, §C.9                                                                                                                          | 7 |

| 19 | Extract from driver c &C 7                                                                                                                             | 8 |

## Chapter 1

# Introduction & Background

Computer Security

.

Cryptography

.

Thesis Structure

#### 1.1 Computer Security

"We already are seeing the first wave of deliberate cyber attacks—hackers break into government and business computers, stealing and destroying information, raiding bank accounts, running up credit card charges, extorting money by threats to unleash computer viruses."—President Bill Clinton.[Gol99]

While it is very laudable for the President of the U.S.A. to say these words, the reality of the situation is that computer security is woefully neglected in the general computing world (the damage that the 'T Love U" virus was able to do being a case in point). Today's computer environment consists of physically distributed personal computers and workstations, connected by networks. Such an environment is inherently difficult to protect.

Arbaugh et al. have pointed out that the integrity of the operating system's kernel cannot be trusted because malicious code can be injected in the bootstrap process[AFS97]. For example, typical PCs can be booted from CDROM, floppy disks or over the network, thus allowing arbitrary code to be run. Some do allow an administrator to set a BIOS (Basic Input Output System) password thus allowing the boot process to continue only if the correct password is entered. However it is not to difficult to remove the password by resetting the BIOS[FW99].

The advantage of software only implementations is that they are inexpensive and easy to deploy. The disadvantage of these implementations is that they provide a very low level of protection for cryptographic variables and, unfortunately, this low level of security is unlikely to change in the future. Vulnerable software ranges from the applications right down to the operating system. Some examples:

#### 1. Operating systems

- scanning memory for encryption keys in Windows NT[SS98].

- Windows NT jump table patching[RC97].

- erroneous permissions of DLL cache on Windows NT 4.0[dil99].

#### 2. Basic system programs

• intercepting shell messages[Hei98].

• buffer overflow in df, eject, login, etc., in IRIX[CER97].

#### 3. Daemons

- buffer overflow in wu-ftpd[CER99c].

- buffer overflow in IIS web server [CER99b].

- bugs in sample files in IIS[wel99].

#### 4. Applications

• buffer overflow in sendmail[CER99a]

#### 5. Network protocols

• flaws in ICMP Router Discover Protocol allowing man-in-the-middle attack[sil99a]

#### 6. Security software

- poor encrypting of shellock[ml99].

- password appraiser sending Windows passwords in the clear on the Internet[mud99]

Such vulnerabilities can be quite serious. They may yield control of the machine to an opponent, crash the system or leak critical information (cryptographic keys). Unfortunately, the main problem is that for most people there is no problem:

"If only more people were aware of the problem. Then I wouldn't have to start off by having to convince them they needed to do something - we could get right down to solving problems" [Ran99]

Users see it as normal for software to contain bugs. Since program correctness is difficult to achieve[Wie93], and as long as features are the major selling point for products, buggy and insecure systems will be the normal state of affairs[CF98]. The simple fact is that no mainstream operating system has the features required to implement proper security policies[LSM+98], and the work involved in performing the necessary redesign from scratch with an operating system containing millions of lines of code would make it prohibitive[Gut00].

This seems to be painting a very bleak picture for someone trying to provide "secure" services to users. How do we address this problem? One approach is to move the cryptography away from the insecurity. In other words, though a user may be running the latest up to date operating system with all the latest bugs and un-patched buffer overflows, none of these can subvert the cryptography. Hence we move the crypto operations and the critical cryptographic keys into hardware.

In [Gut00] Gutmann does this by using an embedded Linux solution running on a RISC processor. At the opposite end of the spectrum, Itoi [Ito00] uses IBM's 4758 cryptographic co-processor [chp] to secure a Kerberos Key Distribution centre. Not one of these approaches use a firmware implementation, they involve downloading a conventional program into an on-board RISC or CISC processor.

#### 1.1.1 Goals

The goals of this work are:

- Investigate the area of cryptographic algorithms, and decide on one algorithm for further investigation.

- Implement this chosen algorithm both in software and firmware.

- Compare the differences in implementation and performance, of the different domains.

- Suggest possible improvements of the different implementations based on experience gained.

### 1.2 Cryptography

#### 1.2.1 A Brief History

"On a day nearly 4000 years ago, in a town near the Nile, a master scribe sketched out the hieroglyphs that told the story of his lord's life — and in doing he opened the recorded history of cryptology". His was not a system of secret writing as the modern world knows, he merely used some unusual hieroglyphics here and there in place of more ordinary ones. The intention was not to make it hard to read the text, but to impart a dignity and authority to it, perhaps in the

same way that a government proclamation will spell out "In the year of Our Lord Nineteen Hundred and Ninety Nine" instead of just "1999." The anonymous scribe may also have been demonstrating his knowledge for posterity. Thus the inscription was not secret writing, but it incorporated one of the essential elements of cryptography: a deliberate transformation of the writing. It is the oldest text known to do so.

In its first 4000 years, Cryptology did not grow steadily, it rose and grew independently in many places, and in most of them it also died with its civilisations. In other places, it survived, embedded in a literature, and from this the next generation could climb to higher levels. But progress was slow and inconsistent. More was lost than retained. Much of the history of cryptology of this time is a patchwork of unrelated items, sprouting, flourishing, withering. Only toward the Western Renaissance does the accreting of knowledge begin to build up a momentum. Modern cryptologywas born among the Arabs. They were the first to discover and write down the methods of breaking codes and ciphers, the word "cipher" itself, comes from the Arabic word for mathematics [Kah96].

#### 1.2.2 The Fundamental Idea of Cryptography

It is possible to transfer or encipher a message or *plaintext* into "an intermediate form" or *ciphertext* in which the information is *present* but *hidden*. Then we can release the transformed message (the ciphertext) without exposing the information it represents.

By using different transformations, we can create many different ciphertexts for the exact same message. So if we select a particular transformation "at random," we can hope that anyone wishing to expose the message ("break" the cipher) can do no better than simply trying all available transformations (or on average half) one-by-one. This is a brute force attack.

A cryptographic "key" is an item of data which is shared among the communicating parties to facilitate cryptographic techniques. This data may include public or secret keys, initialisation values, and additional non-secret parameters. The are generally classified according to Table 1.1. Hence a "symmetric" algorithm uses a single key for encryption and decryption, and similarly, an "asymmetric" algorithm uses a public and private key for decryption and encryption respectively.

The difference between intermediate forms is the *interpretation* of the ciphertext data. Different ciphers and different keys will produce different inter-

| Term                    | Meaning                                              |

|-------------------------|------------------------------------------------------|

| private key, public key | paired keys in an asymmetric cryptographic system    |

| symmetric key           | key in a symmetric (single-key) cryptographic system |

| secret                  | adjective used to describe private or symmetric key  |

Table 1.1: Key Classification

pretations (different plain-texts) for the exact same ciphertext. The uncertainty of how to interpret any particular ciphertext is how information is "hidden."

Naturally, the intended recipient needs to know how to decipher the intermediate form back into the original message, and needs to receive the decryption key in a secure manner. The latter is the key distribution problem.

As an example, while attending Secondary School is was common practice to encipher messages to pass to friends in "study". Key Distribution was easy: drop the key into the other party's desk while entering study. Unfortunately, in a real system, key distribution is not so such an easy task, and will be dealt with later.

By itself, ciphertext is literally meaningless, in the sense of having no one clear interpretation. In so-called perfect ciphers, any ciphertext (of appropriate size) can be interpreted as any message, just by selecting an appropriate key. In fact, any number of different messages can produce exactly the same ciphertext, by using the appropriate keys. In other ciphers, this may not always be possible, but it must always be considered. To attack and break a cipher, it is necessary to somehow confirm that the message we generate from ciphertext is the message which was originally sent (i.e., we know the plaintext).

#### 1.2.2.1 The Single Transformation

The single transformation cipher is a simple substitution cipher: a streaming or repeated letter-by-letter application of the same transformation. That "transformation" is the particular arrangement of letters in the second column, for example, a simple permutation of the alphabet. There can be *many* such arrangements. But in this case the key *is* that particular arrangement. We can copy it and give it to someone and then send secret messages to them. But if that sheet is acquired – or even copied – by someone else, the enciphered messages would be exposed. This means that we have to keep the transformation secret.

One of the earliest descriptions of this method appears in the  $K\bar{a}ma$ - $s\bar{u}tra$ ,

a text written in the fourth century AD by the Brahmin scholar Vātsyāyana, based on manuscripts dating back to the fourth century BC. The  $K\bar{a}ma$ -s $\bar{u}tra$  recommends that women should study 64 arts, such as cooking, dressing, massage and the preparation of perfumes. Number 45 on the list is mlecchita- $vikalp\bar{a}$ , the art of secret writing, advocated in order to help women conceal the details of their liaisons. One of the first documented uses of a substitution cipher for military purposes appears in Julius Caesar's  $Gallic\ Wars$ . The substitution replaced Roman letters with Greek letters, rendering the message unintelligible to the enemy ([Sin99, pp9-10]).

#### 1.2.2.2 Many Transformations

Now suppose we have a full notebook of lined pages, each of which contains a different arrangement in the second column and each page is numbered. Now we just pick a number and encipher the message using that particular page. That number thus becomes our key, which is now a sort of numeric shorthand for the full transformation. So even if the notebook is exposed, someone who wishes to expose our message must try about half of the transformations in the book before finding the right one. Since exposing the notebook does not immediately expose our messages, maybe we can leave the notebook unprotected. We also can use the same notebook for messages to different people, and each of them can use the exact same notebook for their own messages to each other. Different people can use the same notebook and yet still cipher messages which are difficult to expose without knowing the right key. Note that there is some potential for confusion in first calling the transformation a key, and then calling the number which selects that transformation also a key. But both of these act to select a particular ciphertext construction from among the many. There are only two of the various kinds of "key" in cryptography.

#### 1.2.2.3 Weak and Strong Transformations

The simple substitution used in the above cipher is very weak, because it "leaks" information: the more often a particular plaintext letter is used, the more often the associated ciphertext letter appears. And since language uses some letters more than others, simply by counting the number of times each ciphertext letter occurs we can make a good guess about which plaintext letter it represents. Then we can try our guess and see if it produces something we can understand. It usually does not take too long before we can break the cipher, even

without having the key. In fact, we develop the ultimate key (the enciphering transformation) to break the cipher.

A "real" cipher will have a far more complex transformation. For example, the usual 64-bit block cipher will encipher 8 plaintext letters at the same time, and a change in any one of those letters will change all 8 letters of the resulting ciphertext. This is still simple substitution, but with a huge alphabet. Instead of using 26 letters, a 64-bit block cipher views each of  $2^{64}$  different block values as a separate letter, which is approximately  $1.8 \times 10^{19}$  "letters."

#### 1.2.2.4 Key-space

Suppose we have 256 (0-255) pages of transformations in the notebook; this means there are exactly 256 different keys we can select from. If we write the number 256 in binary we get "1000000000"; here the leftmost 1 represents 1 count of  $2^8$ . Or, we can compute the base 2 logarithm by first taking the natural log of 255 (about 5.545) and dividing that by the natural log of two (about 0.693); this result is also 8. So we say that having 256 key possibilities is an "8 bit" key-space. If we choose one of the 256 key values at random, and use that transformation to encipher a message, someone wishing to break our cipher should have to try about 128 deciphering operations before happening upon the correct one. The effort involved in trying, on average, 128 deciphering operations (a brute force attack) before finding the right one, is the design strength of the cipher.

If our notebook had 65,536 pages or keys (instead of just 256), we would have a "16 bit" key-space. Notice that this number of key possibilities is 256 times that of an "8 bit" key-space, while the key itself only has 8 bits more than the "8 bit" cipher. The strength of the "16 bit" cipher is the effort involved in trying, on average, 32,768 deciphering operations before finding the right one.

The idea is the same for a modern cipher: We have a machine which can produce a huge number of transformations between plaintext and ciphertext, and we select one of those transformations with a key value. Since there are many, many possible keys, it is difficult to expose a message, even though the machine itself is not secret. And many people can use the exact same machine for their own secrets, *without* revealing those secrets to everyone who has such a machine.

#### 1.2.2.5 Digital Electronic Ciphering

One of the consequences of having a computer for ciphering is that it operates very, very fast. This means that someone trying to break the cipher (the "cryptanalyst"), can try a lot more possibilities than they could with a pen and paper.

Assume that we have a perfect (symmetric key) algorithm. By perfect, we assume that there is no better way to break the crypto-system other than trying every possible key in a brute-force attack.

To launch this attack, a cryptanalyst needs a small amount of ciphertext and the corresponding plaintext; a brute-force attack is a known-plaintext attack<sup>1</sup>. For a block cipher (see §1.2.11), the cryptanalyst would need a block of ciphertext and corresponding plaintext: generally 64 bits. Assuming a computer can try a million keys a second, it will take 2285 years to find the correct key[Sch96, p151]. If the key is 64 bits long, then it will take the same computer about 585,000 years to find the correct key among the 2<sup>64</sup> possible keys. If the key is 128 bits long, it will take 10<sup>25</sup> years. The universe is only 10<sup>10</sup> years old, so 10<sup>25</sup> years is a long time. With a 2048-bit key, a million million-attempts-per-second computers working in parallel will spend 10<sup>597</sup> years finding the key. By that time the universe will have long collapsed or expanded into nothingness.

A brute- force attack is tailor made for parallel processors. Each processor can test a subset of the key-space. The processors do not have to communicate among themselves; the only communication required at all is a single message signifying success. There are no shared memory requirements. It is easy to design a machine with a million parallel processors, each working independent of the others.

In 1994, Michael Wiener decided to design[Wei93][Wei94] a brute-force cracking machine. He designed the machine for the Data Encryption Standard (DES)<sup>2</sup>[oST93] algorithm, but the analysis holds for almost any symmetrical key algorithm. He designed specialised chips, boards, and racks. He estimated prices and discovered that for \$1 million, someone could build a machine that could crack a 56-bit DES key in an average of 3.5 hours (results guaranteed in 7 hours). And that the price/speed ratio is linear. Table 1.2 generalises these

<sup>&</sup>lt;sup>1</sup>By trying all possible keys, the ciphertext will eventually be decoded to the plaintext. Thus the confidentiality of all transmissions hinges on the choosing a key length that can be "cracked" in an "impossibly" long time.

<sup>&</sup>lt;sup>2</sup>Known at the Data Encryption Algorithm by ANSI and DEA-1 by the ISO, has been a worldwide standard for 25 years. The standard UNIX password system uses DES with variations intended to discourage brute-force cracking. See [Sch96, pp265-294] for details.

| Cost   | 40               | 56            | 64          | 80           | 128                      |

|--------|------------------|---------------|-------------|--------------|--------------------------|

| \$100K | 2 seconds        | 35 hours      | 1 year      | 70,000 years | $10^{19} \text{ years}$  |

| \$1M   | .2 seconds       | 3.5 hours     | 37 days     | 7000 years   | $10^{18} \text{ years}$  |

| \$10M  | .02 seconds      | 21 minutes    | 4 days      | 700 years    | $10^{17} \mathrm{years}$ |

| \$100M | 2 milliseconds   | 2 minutes     | 9 hours     | 70 years     | $10^{16}\mathrm{years}$  |

| \$1G   | .2 milliseconds  | 13 seconds    | 1 hour      | 7 years      | $10^{15}\mathrm{years}$  |

| \$10G  | .02 milliseconds | 1 second      | 5.4 minutes | 245 days     | $10^{14}\mathrm{years}$  |

| \$100G | 2 microseconds   | .1 second     | 32 seconds  | 24 days      | $10^{13}\mathrm{years}$  |

| \$1T   | .2 microseconds  | .01 second    | 3 seconds   | 2.4 days     | $10^{12}\mathrm{years}$  |

| \$10T  | .02 microseconds | 1 millisecond | .3 second   | 6 hours      | $10^{11}\mathrm{years}$  |

Table 1.2: Average Time Estimates for a Hardware Brute -Force Attack in 1995

numbers to a variety of key lengths. Moore's Law, however states: Computer processing power doubles approximately every 18 months.<sup>3</sup> This means that the costs go down roughly by a factor of 10 every 5 years; what cost \$1 million in 1995 will cost a mere \$100,000 today. Pipelined computers might do even better[HA94]. For 56-bit keys, these numbers are within the budgets of most large companies and many criminal organisations. The military budgets of most industrialised nations can afford to break 64 bit keys. Breaking an 80 bit key is still beyond the realm of possibility, but if trends continue, that will change within the next 25 years. In cryptography is is wise to be pessimistic.

Without special-purpose hardware and massively parallel machines, brute-force attacks are significantly harder. A software attack is about a thousand times slower than a hardware attack and is generally measured in MIPS-years: a million-instructions-per-second processor running for one year, which is about  $3 \star 10^{13}$  instructions executed. A 200-MHz Pentium is about a 50-MIPS machine. Unfortunately the "MIPS-year" is often both miscalculated and misused. Silverman tries to clear up this confusion [Sil99b], demonstrating how the "MIPS-Year" can be applied as a measurement of the amount of effort required to break, and compare the "strength" of, cryptographic keys.

The real threat of a software-based brute-force attack is not that it is certain, but that it is "free". It costs nothing to set up a microcomputer to test possible keys whenever it is idle (In a typical educational institution for example all the student-accessible PCs are guaranteed to be idle for at least 10 hours day). If it finds the key — great; if it doesn't, then nothing is lost (arguments about the electricity usage not withstanding). It costs nothing to set up an entire network

<sup>&</sup>lt;sup>3</sup>This increase in computing speed results mainly from the increasing miniaturisation of components.

to do that. In 1991 an experiment with DES used the collective idle time of 40 workstations to test 2<sup>34</sup> keys in a single day[GO91]. At this speed it would take 4 million days to test all keys. If enough people try attacks like this, then someone somewhere will get lucky.

#### 1.2.3 What Cryptography Can do

Potentially, cryptography can hide information while it is in transit or storage<sup>4</sup>. In general, cryptography can:

- Provide Secrecy

- Authenticate that a message has not changed in transit

- Implicitly authenticate the sender

Cryptography hides words: At most it can only hide talking about contraband or illegal actions. In countries with "freedom of speech", we normally expect crimes to be more than just "talk."

Cryptography can kill. Not in the same way as a knife can kill, but as part of a system or process. It could be argued that the Japanese Pacific fleet lost the battle at Midway because of cryptography. They assumed that their crypto-systems were unbreakable, which was not the case, as the Americans were reading their traffic. The American cryptanalysts were almost certain that the main attack would come at Midway (they had deciphered messages relating to "AF" which they were pretty sure was an indicator for Midway on a partially solved map grid) but they needed proof. So they sent out a plain language message saying that the fresh-water distillation plant on Midway had failed. Several days later the American cryptanalysts deciphered a Japanese intercept stating that "AF" was short of fresh water. Now they were sure where the attack would come [Kah96, p569].

Cryptography, in general, is defensive, and can *protect* ordinary commerce and ordinary people.

In the face of the snowballing bigness of the institutions of globalised human life, we must reserve privacy rights explicitly so that we may misrepresent ourselves to those against whom we have no

<sup>&</sup>lt;sup>4</sup>No matter how secure an algorithm, if it is part of a badly implemented "crypto-system" then it does nothing more than give the user a deluded sense of security.

other defence, against those for whom our name is but a label on data collected without our consent[Gee99].

Cryptography can hide secrets, either from others, or during communication. There are many good and non-criminal reasons to have secrets: certainly those engaged in commercial research and development have "secrets" they must keep. Professors and writers may want to keep their work private, until an appropriate time. Negotiations for new jobs are generally private, at least we might prefer that detailed discussions not be exposed. One possible application for cryptography is to secure on-line communications between work and home, perhaps leading to a society-wide reduction in commuting.

#### 1.2.4 What Cryptography Can Not do

Cryptography can only hide information after it is encrypted and while it remains encrypted. But secret information generally does not start out encrypted, so there is normally an original period during which the secret is not protected. And secret information generally is not used in encrypted form<sup>5</sup>, so it is again outside the cryptographic envelope every time the secret is used.

Secrets are often related to public information, and subsequent activities based on the secret can indicate what the secret is.

Cryptography simply cannot protect against:

- Informants.

- Undercover Spying.

- Bugs (in both system implementation and eavesdropping devices).

- Photographic evidence.

- Testimony.

It is a mistake to imagine that cryptography alone could protect most information against "Big Brother" or potentially of more grave concern, many "little brothers" [Gee99]. Cryptography is only a small part of the protection needed for "absolute" secrecy.

$<sup>^5\</sup>mathrm{P.G.P.}$  the email encryption package has a mode of operation whereby the received, encrypted, email can be displayed on the screen, without being stored on disk in its un-encrypted form.

#### 1.2.5 Problems with Keys

The physical key model reminds us of various things that can go wrong with keys:

- We can lose our keys.

- We can forget which key is which.

- We can give a key to the wrong person.

- Somebody can steal a key.

- Somebody can pick the lock.

- Somebody can go through a window.

- Somebody can break down the door.

- Somebody can ask for entry, and unwisely be let in.

- Somebody can get a warrant, then legally do whatever is required.

- Somebody can burn down the house, thus making the key irrelevant.

Even absolutely perfect keys cannot solve all problems, nor can they guarantee privacy. And how do we get a key to the correct place/person, are we sure that the person is who they say they are? Indeed, when cryptography is used for communications, generally at least two people know what is being communicated. So either party could reveal a secret:

- By accident.

- To someone else.

- Through third-party eavesdropping.

- As revenge, for actions real or imagined.

- For payment.

- Under duress.

- In testimony.

In summary, when it is substantially less costly to acquire the secret by means other than a technical attack on the cipher, cryptography has pretty much succeeded in doing what it can do.

#### 1.2.6 Strength

Key-space alone only sets an *upper limit* to cipher strength; a cipher can be *much* weaker than it appears. An in-depth understanding or analysis of the design may lead to "shortcuts" in the solution. Perhaps a few tests can be designed, each of which eliminates vast numbers of keys<sup>6</sup>, quite possibly reducing the effort required by the attacker (called the Opponent) by orders of magnitude such that a brute-force attack is now feasible. This process is called cryptanalysis.

We understand strength as the ability to *resist* cryptanalysis. But this makes "strength" a negative quality (the *lack* of any practical attack), which we cannot measure. We can *infer* the "strength" of a cipher from the best *known* attack. We can only hope that the Opponent does not know of something better.

Every user of cryptography should understand that all known ciphers are at least *potentially* vulnerable to some unknown technical attack<sup>7</sup>. And if such a break does occur, there is absolutely no reason that we would find out about it. However, a direct technical attack may be one of the least likely avenues of exposure.

#### 1.2.7 System Design and Strength

Cryptographic design may seem as easy as selecting a cipher from a book of ciphers. But ciphers, are only part of a secure encryption system. It is common for a cipher system to require cryptographic design beyond simply selecting a cipher, and such design is much tricker than it looks.

The use of an unbreakable cipher does *not* mean that the encryption system will be similarly unbreakable. A prime example of this is the man-in-the-middle attack on public-key ciphers (see §1.2.12). Public-key ciphers require that one use the correct key for the desired recipient. The correct key must be known to cryptographic levels of assurance, or the key itself becomes the weakest link in the system; Suppose an Opponent can get us to use his key instead of the right one (perhaps sending a faked message saying "Here is my new key"). If he can do this to both ends, and also intercept all messages between them (which is conceivable, since Internet routing is not secure), the Opponent can sit "in the middle." He can decipher each message (now in one of his keys), then reencipher that message in the correct user key, and send it along. So the users

<sup>&</sup>lt;sup>6</sup>"Idea", the algorithm used in P.G.P., has a number of "weak" keys. [Sch96, p323][DGV94b]

<sup>7</sup>The "One-Time Pad" cipher has as many values in the key as the plaintext. This is the source of its *perfect* security. It is essential that no portion of the key *ever* be reused for another encryption (hence the name), otherwise current cryptanalysis can break the cipher.

communicate, and no cipher has been broken, yet the Opponent is still reading the conversation. Such are the consequences of system design error.

#### 1.2.8 Cryptanalysis versus Subversion

Cryptanalysis is hard; it is often tedious, repetitive, and very expensive. Success is never assured, and resources are always limited. Consequently, other approaches for obtaining the hidden information (or the key) can be more effective.

Approaches other than a direct technical attack on ciphertext include getting the information by cunning, outright theft, bribery, or intimidation. The room or computer could be bugged, network sniffers could be installed on "rooted" computers, secretaries subverted, files stolen, etc. Most information can be obtained in some way other than "breaking" ciphertext.

When the effort required to break the cipher greatly exceeds the effort required to obtain the same information in another way, the cipher is probably strong enough. And the mere fact that information has escaped does not necessarily mean that a cipher has been broken.

It is interesting to note that virtually every crypto-system invented before the 1940s was systematically overcome by applying Shannon's information theory of secrecy systems, first published in 1949[Sha49]. All of the systems had been broken piecemeal before that time, but for the first time, cryptanalysts had a general way to attack all crypto-systems. Only two systems remain impervious to this attack, the "One Time Pad" and Public Key Systems (detailed in §1.2.12).

#### 1.2.9 Secret Ciphers

Although cryptanalysis might succeed even if the ciphering process was unknown, we would certainly expect that this would make the Opponent's job much harder. It can thus be argued that the ciphering process *should* remain secret. Military cipher systems are not actually published, although it would be foolish of the military not to assume that any competent Opponent will obtain this information through other channels. Military Ciphers are still designed with the following ideals which were deduced by Kerchoffs in 1883[Kah96, p235]:

<sup>&</sup>lt;sup>8</sup>A underground term used by a "cracker" to describe a machine that has been successfully broken in to, and which is now under the control of the cracker and, more than likely, his cohorts.

- 1. The system should be, if not theoretically unbreakable, unbreakable in practice.

- 2. Compromise of the system should not inconvenience the correspondents.

- 3. The key should be rememberable without notes and be easily changeable.

- 4. The cryptograms should be transportable by telegraph.

- 5. The apparatus or documents should be portable and operable by a single person.

- 6. The system should be easy, neither requiring knowledge of a long list of rules nor involving mental strain.

Over time, these requirements have been rephrased, and qualities that lie implicit have been made explicit. But any modern cryptographer would be very happy if any cipher fulfilled all six.

In commercial cryptography we normally assume that the Opponents will know every detail of the cipher (excluding the key, of course). There are several reasons for this:

- It is common for a cipher to have unexpected weaknesses which are not found by its designers. If the cipher design is kept secret, it cannot be examined by other parties, and so weaknesses may not be publicly exposed, and could be exploited in practice.

- If a cipher itself is a secret, then that secret is increasingly compromised by making it available for use. For a cipher to be used, it must be present at various locations, and the more widely it is used, the greater the risk of the secret being exposed. So whatever advantage there may have been in keeping the cipher-mechanism secret will be lost, and the Opponents eventually will have the same advantage as they would have had from public disclosure.<sup>9</sup>

There is another level of secrecy here, and that is the trade secrecy involved with particular software designs. Few large companies are willing to release source code for their products without some serious controls. While the crypto routines themselves presumably might be patented, releasing that code alone

<sup>&</sup>lt;sup>9</sup>Only now the cipher designers may comfort themselves with the dangerous delusion that they have an advantage over their opponents.

probably would not support a thorough security evaluation as the years of research and conclusions from that research have not been made available for scrutiny. People are fallible, thus conclusions taken from research may be in error. Source code might reasonably be made available to customers under a non-disclosure agreement, but this will not satisfy everyone. And while it might seem nice to have all source code available for free, this will not support an industry of continued cipher design and development. However the Advanced Encryption Standard (AES, §1.2.14) program is hoping to address this issue by standardising on an algorithm for the future that is free, and that has received as much exposure and cryptanalysis as possible. As the minimum key length of AES is 128 bits, it is envisaged that AES will be "Secure Enough" [BDR+96] for everyone's needs, assuming no better attack than brute force (Figure 1.2). But who knows, maybe some of the more powerful security agencies have already compromised all of the candidates.

#### 1.2.10 Hardware vs Software Ciphers

Currently, most ciphers are implemented in software, that is, by a program of instructions executed by a general-purpose computer. Normally, it is cheaper to implement an algorithm in software, but hardware can run faster, and nobody can change its operation through the use of software. Of course, there are levels to hardware, from microprocessors (which thus require significant interface software) to external boxes with communications lines running in and out. Anyone trying to decide whether to deploy a software or hardware implementation has to consider the security risks, their expense along with the following issues (amongst others):

- Software, especially in a multi-user system, is almost completely insecure ([LSM+98]). This may not be an issue for home users, and real solutions here may depend upon secure operating systems.

- Hardware represents a capital expense, and is extremely inflexible.

- Software operates more efficiently on blocks of data than streams of data.

- It is more expensive both in terms of time and monetary value to replace (crypto) hardware than (crypto) software <sup>10</sup>.

$<sup>^{10}\</sup>mathrm{See}$  http://www.ireland.com/newspaper/finance/2000/0315/fin18.htm for a current example

This rest of this work will take the approach of putting the algorithm, and even more importantly, the key-authentication-key, into firmware. Our primary requirement being the capability to instantiate a secure communications channel between two hosts. This approach gives higher security and speed at a higher (monetary) cost, if, and only if, implemented correctly [LSM+98]. The ideal being a "computational device that can be trusted to execute its programming correctly, despite physical attack" [SW99]

#### 1.2.11 Block & Stream Ciphers

There are two basic types of encryption algorithms: block ciphers and stream ciphers. A block cipher is one in which a block of plaintext is treated as a whole and used to produce a block of ciphertext of equal length. A stream cipher is one that encrypts a digital data stream one bit or byte at a time. While all ciphers are classified in this fashion, in truth most algorithms can be either: blocks can be formed from streams and vice versa [Sch00].

#### 1.2.12 Public Key Ciphers

Public key ciphers (and their related public key exchange algorithms) are generally block ciphers, with the unusual property that one key is used to encipher, while a different and apparently unrelated key is used to decipher a message. So if one of the keys is kept private, the other key (the "public" key) can be released "into the wild", and anyone can use that to encipher a message to us. Then our private key can be used to decipher any such messages. An interesting side effect of this scheme is that someone who enciphers a message and sends it to us cannot decipher their own message even if they want to.

The prototypical public key cipher is RSA, which uses large numeric values as keys. These numbers may contain 1,000 bits or more (over 400 decimal digits), in which each and every bit is significant. The key-space is much smaller, however, because there are very severe constraints on the keys; not just any random value will do. So a 1,000-bit public key may have a brute-force strength similar to a 128-bit secret key cipher.

Because public key ciphers operate on huge values, they are very slow, and so are normally used just to encipher a random message key. The message key is then used by a conventional secret key cipher which actually enciphers the data. At first glance, public key ciphers apparently solve the key distribution problem (mentioned earlier in §1.2.5 this problem is first acknowledged in literature in [DH76]). But in fact they also open up the new possibility of a man-in-themiddle attack or the user authentication problem.

How do you know that the key belongs to who you think it does? Still a research problem.[Ros00]

To avoid this, it is necessary to assure that one is using exactly the correct key for the desired user. This requires authentication (validation or certification) via some sort of secure channel, and that can take as much effort as a secure secret key exchange. A man-in-the-middle attack is extremely worrisome, because it does *not* involve breaking any cipher, which means that all the efforts spent in cipher design and analysis and mathematical proofs and public review would be completely irrelevant.

#### 1.2.13 Quantum Leap

Quantum computing is an area where things get either very exciting or very weird, depending on your point of view. It is outside the scope of this work to go into quantum computing in any detail. Suffice it to say that for long term security, the mere existence of quantum computing, means that Public Key Encryption systems are already broken. Currently, with quantum computing, the only type of message that it is known how to share securely, is a completely random string of bits. However, a random string is the perfect key on which to base standard symmetric key cryptography schemes. By using a system in which the integrity and secrecy of the key is guaranteed by the laws of nature we are getting closer to realisation of the "ideal" cipher (§1.2.9). Unfortunately, for the moment it is unlikely this type of cryptography will be practical for the foreseeable future [Sch96][Sin99][SR00].

#### 1.2.14 The Advanced Encryption Standard (AES)

On January 2, 1997<sup>11</sup>, National Institute of Standards and Technology (NIST) announced the initiation of the AES development effort and made a formal call for algorithms on September 12, 1997. The call stipulated that the AES would specify an unclassified, publicly disclosed encryption algorithm(s), available royalty-free, worldwide. In addition, the algorithm(s) must implement

<sup>&</sup>lt;sup>11</sup>This section is an excerpt from http://www.nist.gov/aes

symmetric key cryptography as a block cipher and (at a minimum) support block sizes of 128-bits and key sizes of 128-, 192-, and 256-bits.

On August 20, 1998, NIST announced a group of fifteen AES candidate algorithms at the First AES Candidate Conference (AES1). These algorithms had been submitted by members of the cryptographic community from around the world. At that conference and in a simultaneously published Federal Register notice, NIST solicited public comments on the candidates. A Second AES Candidate Conference (AES2) was held in March 1999 to discuss the results of the analysis conducted by the global cryptographic community on the candidate algorithms. The public comment period on the initial review of the algorithms closed on April 15, 1999. Using the analyses and comments received, NIST selected five algorithms from the fifteen.

The AES finalist candidate algorithms are MARS, RC6, Rijndael, Serpent, and Twofish. NIST has developed a Round 1 Report describing the selection of the finalists.

These finalist algorithms will receive further analysis during a second, more in-depth review period prior to the selection of the final algorithm(s) for the AES Federal Information Processing Standard (FIPS). NIST solicits comments on the remaining algorithms through May 15, 2000. Comments and analysis are actively sought by NIST on any aspect of the candidate algorithms, including, but not limited to, the following topics: cryptanalysis, intellectual property, cross-cutting analyses of all of the AES finalists, overall recommendations and implementation issues. An informal AES discussion forum is also provided by NIST for interested parties to discuss the AES finalists and relevant AES issues.

#### 1.3 Thesis Structure

In Chapter 2, Encryption Algorithm, an algorithm is selected after first spending some time on issues such as algorithm type, encryption modes, and their implications. Then the algorithm is examined in detail to try to get a "feel" for the difficulties in the area. As ciphers can be used in different ways, the main "modes" of operation are examined and a decision is made how to deploy the selected algorithm. Without secure keys, the "system" can easily be compromised so key generation issues are investigated. This is a whole area of study in its own right, as generation of cryptographically secure random numbers is inherently more difficult than one would assume. Finally the reference software

implementation is examined in detail

In Chapter 3, *Firmware*, the technology and different development environments are introduced and examined. A development environment is chosen. The difference between the software and firmware "domains" are highlighted and explored. A firmware implementation of the algorithm selected in Chapter 2 is presented.

In Chapter 4, *Deployment*, the software implementation is packaged as a "device driver" and uses the reference code implementation covered in Chapter 2. The firmware implementation covered in Chapter 3 is packaged as an equivalent cryptographic device. Significant extra circuitry (scaffolding) is required to actually realise a functioning firmware implementation. Building on the work of the previous two chapters, a stable and functional solution is realised.

Chapter 5, Results and Conclusions, details the results of tests performed on the solution, presents a discussion on the achievements of the work and compares the differences between the software and firmware implementations. Some further work outside the scope of this thesis is discussed which would extend the work in interesting and useful directions.

### Chapter 2

## **Encryption Algorithm**

Introduction

.

**Algorithm Selection**

.

3way: The Basic Building Blocks

.

Cipher Modes Explained

.

Reference Code - A short tour

.

Conclusion

#### 2.1 Introduction

In §1.2.11 block ciphers were introduced. The primary motivation for following this path is, in the real world, block ciphers seem to be more general and stream ciphers seem to be easier to analyse mathematically. Otherwise, the differences are in the implementation. Stream ciphers only encrypt and decrypt data one bit at a time and are not really suitable for software implementation. Block ciphers can be easier to implement in software. On the other hand stream ciphers can be more suitable for hardware implementation because they can be implemented very efficiently in silicon. These are important considerations. It makes sense for a hardware encryptor to encrypt each bit on a digital communications channel as it passes. This is what the device sees. On the other hand it makes no sense for a software encryption device to encrypt each individual bit separately. ([Sch96, pp210-211])

As can be seen from §1.2.10. The requirements are to prototype an algorithm in software, then proceed to implement it in hardware. This is to maintain compatibility with the software algorithm and can also give a more a more secure system by virtue of the Key-Encryption-Key [Smi97, pp107-108]being only in silicon and there being no way to retrieve the key other than destroying the chip. Though there are other reasons covered in [LSM+98, Section 3.2] why a hardware cryptographic device may not be as ideal as it sounds. The primary one being, the operating system can be instructed not to use the cryptographic device, thus nullifying all our efforts.

### 2.2 Algorithm Selection

In choosing an algorithm there are several alternatives:

- 1. Write our own, based on the belief that our cryptographic ability is second-to-none.<sup>1</sup>

- 2. Choose a published algorithm, based on the belief that a published algorithm has been scrutinised by many cryptographers; if no one has broken it, then it must be good.

<sup>&</sup>lt;sup>1</sup>The Japanese PURPLE system is a classic in this regard. Allied cryptographers, never saw a PURPLE machine and yet still managed to break the cipher.

3. Trust a manufacturer, the government, a private consultant to write one.<sup>2</sup>

All of these alternatives are problematic. The second option seems to be the most sensible, given that creating good encryption algorithms is hard[Sch99c] [Cur][Sch99b] and that the last option quite often can prove to be the worst choice:

It is not unusual for people who sell or promote products to claim that their product is the solution to all of your problems but, unfortunately, in information protection, no product can solve all of your problems.[Coh97, p8]

See [Sch99a] and [Cur] for discussions on reasons why this might be. Though Terry Ritter has a very interesting perspective in [Rit99] and the response it generated in [Rit00]. Of course, the glaring problem in deciding that item 2 above is best, is of course that we do not know the abilities of the various military cryptanalysis organisations and probably never will. They may have several unpublished attacks against some, or indeed all published algorithms. The debate on this precise topic can go on for ever, one can argue that the reason the NSA is so set against export of strong crypto is that they have not yet figured out how to break it (other than brute force), thus using any algorithm they do not allow to be exported is safe. The counter is that they already can break them but just do not want to publicise this fact. For example, at the USENIX Security symposium in August 1999<sup>3</sup> the National Security Agency (NSA)<sup>4</sup> had a minimum of two representatives in the front row at every session. Who knows which session they were actually interested in?<sup>5</sup>

So, we decide to go with well published algorithms for the clear advantages they provide. Now we have to decide to go with a public-key system or a symmetric key system, (there are other systems/algorithms not mentioned here see [Kal93] for a more detailed discussion) both provide "confidentiality" and "Key management" which are our primary requirements. We turn to Schneier [Sch96, page 216] for inspiration:

Public-key cryptography and symmetric cryptography are different sorts of animals; they solve different sorts of problems. Symmetric

$<sup>^2 \</sup>rm See\ http://www.ireland.com/newspaper/finance/2000/0315/fin18.htm, the French Banks trusted a manufacturer.$

<sup>&</sup>lt;sup>3</sup>http://www.usenix.org/publications/library/proceedings/sec99/

$<sup>^4</sup>$ http://www.nsa.gov

<sup>&</sup>lt;sup>5</sup>These questions arose from a conversation that took place in the lobby of the Marriot Hotel, Wednesday evening 25'th of August 1999, during the 8th USENIX Security Symposium.

cryptography is best for encrypting data. It is orders of magnitude faster and is not susceptible to chosen-ciphertext attacks. Public-key cryptography can do things that symmetric cryptography can't; it is best for key management and a myriad of protocols...

The choice seems clear: a symmetric system it is, as our main thrust is data encryption. Again Schneier helps out, with a comprehensive (though maybe a bit dated) analysis of the current range of usable block ciphers. DES was the first candidate for rejection as it is no longer considered "secure enough" [HA94]. A selection of other algorithms were ruled out because of either security concerns, patent restrictions or speed. I was left with the following list:

- LOKI91[BKPS93]

- IDEA [Lai92]

- CAST[Ada94][AT93]

- Blowfish[Sch94a][Sch94b]

- 3-Way[Dae95][DGV94a]