#### **Waterford Institute of Technology**

Institiúid Teicneolaíochta Phort Láirge

\_\_\_\_\_

# Improving the Reliability and Performance of FlexRay Vehicle Network Applications Using Simulation Techniques

Robert Shaw B.Sc. (Hons)

M.Sc.

Supervisor: Brendan Jackman B.Sc., M.Tech.

Submitted to the Waterford Institute of Technology Awards Council, 27 May 2009.

#### **ACKNOWLEDGEMENTS**

#### Acknowledgements

I would like to thank the following people for all their support and help over the past two years of this project. Without them this thesis would not be possible.

Firstly I would like to thank Mr. Brendan Jackman for all his encouragement, guidance and enthusiasm throughout this project.

I would also like to thank my fellow group members during the time span of this project, for all their help, guidance and advice:

- Frank Walsh, Group Supervisor, Department of Computing, Maths and Physics,

Waterford Institute of Technology

- David Power, Group Supervisor, Department of Computing, Maths and Physics,

Waterford Institute of Technology

- Gareth Leppla, Group Member, Department of Computing, Maths and Physics,

Waterford Institute of Technology

- Richard Murphy, Group Member, Department of Computing, Maths and Physics, Waterford Institute of Technology

- John Walsh, Group Member, Department of Computing, Maths and Physics, Waterford Institute of Technology

I would also like to thank my friends for all their support and patience while I undertook this project.

Special thanks go to Gillian Chester who showed great patience, support and encouragement throughout this project.

I would lastly and most importantly like to thank my parents who were more of a help than they will ever know.

#### DECLARATION

#### **Declaration**

| I, Robert Shaw, declare that this thesis is submitted by me in partial fulfilment of    |

|-----------------------------------------------------------------------------------------|

| the requirement for the degree M.Sc., is entirely my own work except where otherwise    |

| accredited. It has not at any time either whole or in part been submitted for any other |

| educational award.                                                                      |

| Signature: |

|------------|

|            |

|            |

|            |

|            |

Robert Shaw,

27 May 2009.

#### **Abstract**

Modern vehicles are becoming more and more sophisticated, with more functions being controlled by a microprocessor unit. As new functions are developed there is not only more of a demand on the control unit, but there is also more demand placed on the communication network(s) within a car. There is also a growing need for fast and dependable networks for new safety features such as X-by-wire applications.

A trend in the automotive industry to make cars more eco-friendly has emerged. As the amount of applications increases then the number of wires within a car increases and this can potentially add a large amount of weight leading to increased fuel consumption. This along with the need for higher performance networks led to the development of the FlexRay protocol.

FlexRay is a newly developed network protocol that is intended to address the current and future needs of the automotive industry. It is backed by many automotive manufacturers and suppliers. As such, FlexRay looks increasingly likely to become the network application of choice for many companies, especially where safety critical systems are implemented.

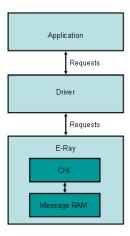

The purpose of this research was to design, implement and test a simulation model of a FlexRay network node. This simulation model could be a benefit to system developers to ensure accurate communication is achieved by tracing the flow of information through a FlexRay-based system and ensuring all timing constraints are met. The model was built using MATLAB, Simulink and SimEvents. The basis of the model was a node that incorporated a separate host microcontroller and communications controller. The communications controller was based on The Bosch E-Ray IP. The simulation model comprised of the application, software driver, communications and physical bus layers of a FlexRay based system. The model was then calibrated against a real world system over a number of different test cases and constraints.

The final part of the research involved running tests to determine if the model that has been built, was built in a correct manner i.e. validation of the simulation model. The model was then evaluated for its ability to carry out its intended role.

#### **Table of Contents**

| Acknowledgements                        | ii       |

|-----------------------------------------|----------|

| Declaration                             | iii      |

| Abstract                                | iv       |

| Table of Contents                       | <i>v</i> |

| Table of Figures                        | <i>x</i> |

| Table of Tables                         | xvi      |

| SECTION I: THESIS OVERVIEW              | 1        |

| CHAPTER 1 . THESIS OVERVIEW             | 2        |

| 1.1 Problem Specification               | 2        |

| 1.2 Research Questions                  | 2        |

| 1.3 Document Layout                     | 3        |

| 1.4 References                          | 5        |

| CHAPTER 2. LITERARY REVIEW INTRODUCTION | 7        |

| 2.1 Scope                               |          |

| 2.2 Terminology                         | 8        |

| 2.3 Criteria for Discussion             | 9        |

| 2.4 Limits of the Review                | 9        |

| CHAPTER 3 . AUTOMOTIVE NETWORKS         | 10       |

| 3.1 Introduction                        |          |

| 3.2 Automotive Networks                 |          |

| 3.3 Networking Type Overview            |          |

| 3.4 Automotive Network Protocols        |          |

| 3.5 Event-Triggered Protocols           |          |

| 3.6 Time-Triggered Protocols            | 23       |

| 3.7 Automotive Network Design           | 30       |

| 3.8 Conclusion                          | 38       |

| 3.9 References                          | 38       |

| CHAPTER 4. FLEXRAY                    | 45  |

|---------------------------------------|-----|

| 4.1 Introduction                      | 45  |

| 4.2 Network Topology                  | 46  |

| 4.3 FlexRay Hardware                  | 47  |

| 4.4 Global Time and Timing            | 48  |

| 4.5 Media Access Control              | 51  |

| 4.6 Frame Format                      | 53  |

| 4.7 Coding & Decoding                 | 56  |

| 4.8 Wakeup                            |     |

| 4.9 Conclusion                        | 64  |

| 4.10 References                       | 64  |

| Chapter 5 . Performance Analysis      | 66  |

| 5.1 Introduction                      | 66  |

| 5.2 System Performance and Analysis   | 66  |

| 5.3 Software Metrics                  |     |

| 5.4 Previous Systems Analysis         | 80  |

| 5.5 Conclusion                        |     |

| 5.6 References                        |     |

| Chapter 6 . E-Ray                     |     |

| 6.1 Introduction                      |     |

| 6.2 Features                          |     |

| 6.3 Components                        |     |

| 6.4 Register Map                      |     |

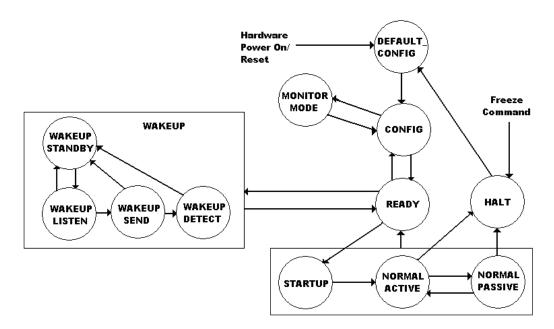

| 6.5 Communication Controller States   | 112 |

| 6.6 Error Handling                    | 116 |

| 6.7 Message Handling                  |     |

| 6.8 Message RAM                       |     |

| 6.9 Filtering and Masking             | 129 |

| 6.10 FIFO                             |     |

| 6.11 Packaging                        |     |

| 6.12 Conclusion                       |     |

| 6.13. References                      |     |

| CHAPTER 7 . DISCRETE EVENT SIMULATION | 136 |

| 7.1 Introduction                      |     |

| 7.2 Systems                           |     |

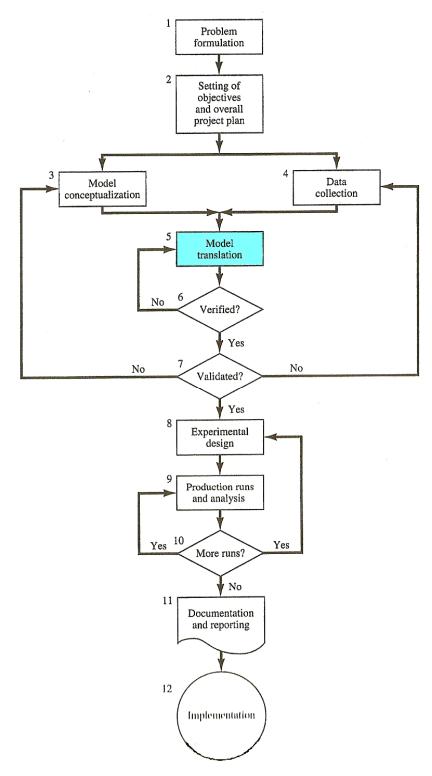

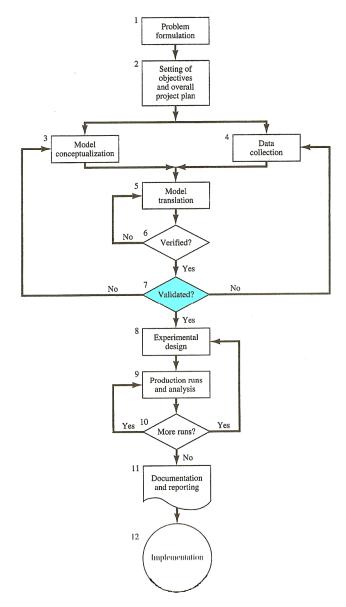

| 7.3 Simulation Process                |     |

| 7.4 Building Models                                     | 140 |

|---------------------------------------------------------|-----|

| 7.5 Validation & Verification                           |     |

| 7.6 Tests and Analysis                                  |     |

| 7.7 Simulation of Queues, Statistics and Random Numbers |     |

| 7.8 Simulation Software                                 |     |

| 7.9 MATLAB, Simulink and SimEvents                      |     |

| 7.10 Simulation Software Selection                      |     |

| 7.11 Conclusion                                         |     |

| 7.11. References                                        | 166 |

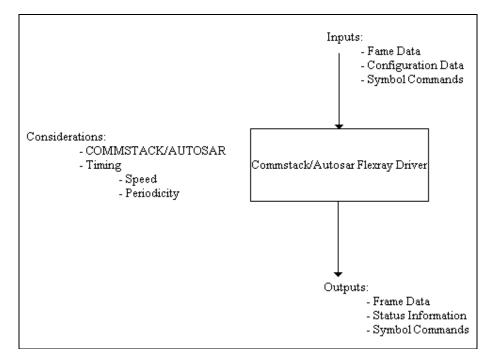

| CHAPTER 8 . FLEXRAY SOFTWARE DRIVERS                    | 170 |

| 8.1 Introduction                                        |     |

| 8.2 COMMSTACK                                           |     |

| 8.3 AUTOSAR                                             |     |

| 8.4 Fujitsu FlexRay Driver                              |     |

| 8.5 Conclusion                                          |     |

| 8.6 References                                          | 182 |

| CHAPTER 9 . LITERARY REVIEW CONCLUSION                  | 185 |

| 9.1 Literary Review Summary                             |     |

| 9.2 Available Literature                                |     |

| 9.3 Areas of Further Study                              | 186 |

| SECTION III: MODEL DEVELOPMENT                          | 187 |

| Chapter 10 . Methodology                                | 188 |

| 10.1 Introduction                                       |     |

| 10.2 Simulation Process                                 |     |

| 10.3 Simulation Process in Relation to the Research     |     |

| 10.4 Conclusion                                         |     |

| 10.6 References                                         | 194 |

| CHAPTER 11 . SIMULATION MODEL DEVELOPMENT               | 195 |

| 11.1 Introduction                                       |     |

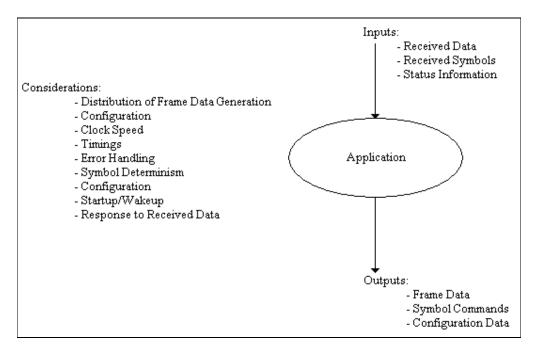

| 11.2 Specification Development Process                  |     |

| 11.3 Simulation Model Specifications                    |     |

| 11.4 Model Metrics                                      |     |

| 11.5 The Model                                          | 212 |

| 11.6 Conclusion                            |     |

|--------------------------------------------|-----|

| 11.7 References                            | 238 |

| Chapter 12 . Verification                  | 240 |

| 12.1 Introduction                          |     |

| 12.2 Verification                          | 24  |

| 12.3 Model Subsystem Debugging             | 243 |

| 12.4 Simulation Model Verification         | 247 |

| 12.5 Model Execution Time                  |     |

| 12.6 Conclusion                            |     |

| 12.7 References                            | 260 |

| SECTION IV: MODEL CALIBRATION & VALIDATION | 26  |

| CHAPTER 13 . CALIBRATION                   | 26  |

| 13.1 Introduction                          |     |

| 13.2 Test Equipment                        | 26- |

| 13.3 Calibration Procedure                 | 275 |

| 13.4 Calibration Test Cases                |     |

| 13.5 Calibration Data & Results            |     |

| 13.6 Conclusion                            |     |

| 13.7 References                            |     |

| Chapter 14 . Validation                    |     |

| 14.1 Introduction                          |     |

| 14.2 Validation Procedure                  |     |

| 14.3 Validation Data Collection            |     |

| 14.4 Validation Review                     |     |

| 14.5 Conclusion                            |     |

| 14.6 References                            |     |

| SECTION V: CONCLUSION                      | 340 |

| CHAPTER 15 . CONCLUSION                    |     |

| 15.1 Introduction                          |     |

| 15.2 Research Summary                      |     |

| 15.3 Research Questions                    | 348 |

| 15.4 Research Conclusions350                                                                   |

|------------------------------------------------------------------------------------------------|

| 15.5 Area of Further Study                                                                     |

| 15.6 References                                                                                |

|                                                                                                |

| SECTION VI: BIBLIOGRAPHY356                                                                    |

|                                                                                                |

| SECTION VII: APPENDICESI                                                                       |

| SECTION VII. ATTEMPLES                                                                         |

|                                                                                                |

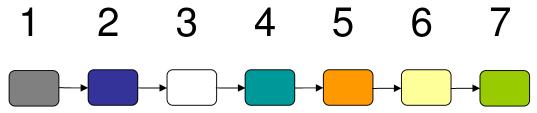

| APPENDIX A: MODEL COLOUR CODINGII                                                              |

|                                                                                                |

| APPENDIX B: MODEL VARIABLES & ATTRIBUTESV                                                      |

|                                                                                                |

|                                                                                                |

| APPENDIX C: THE MODELXVI                                                                       |

|                                                                                                |

| Source CodeXVII                                                                                |

|                                                                                                |

| APPENDIX D: TECHNICAL PAPERSXVIII                                                              |

|                                                                                                |

| 2008 IEEE International Symposium on Industrial Electronics, 30 June - 2 July 2008, Cambridge, |

| United Kingdom 'An Introduction to FlexRay as an Industrial Network' Robert Shaw, Brendan      |

| Jackman XIX                                                                                    |

### **Table of Figures**

| FIGURE 3.1: COMPUTER COMPONENTS AND POSSIBLE CONNECTIONS                             | 11  |

|--------------------------------------------------------------------------------------|-----|

| FIGURE 3.2: EVENT-TRIGGERED AND TIME-TRIGGERED NETWORK PATTERNS                      | 13  |

| FIGURE 3.3: AUTOMOTIVE NETWORK APPLICATIONS                                          | 15  |

| FIGURE 3.4: AUTOMOTIVE NETWORKS FUNCTIONALITY BREAKDOWN                              | 15  |

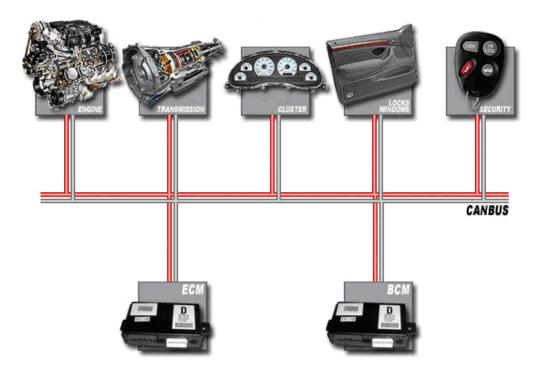

| Figure 3.5: CAN Bus                                                                  | 17  |

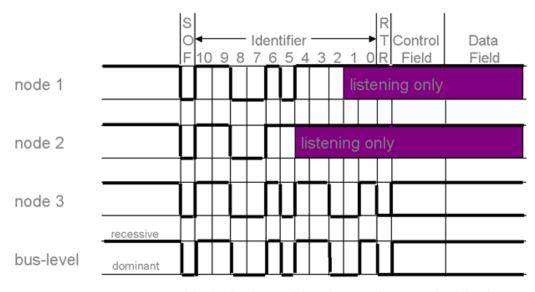

| FIGURE 3.6: CAN BUS ARBITRATION                                                      | 18  |

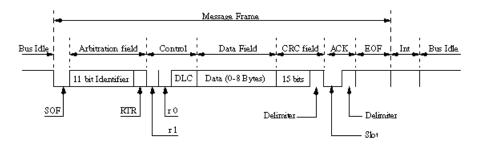

| FIGURE 3.7: CAN STANDARD FRAME FORMAT                                                | 18  |

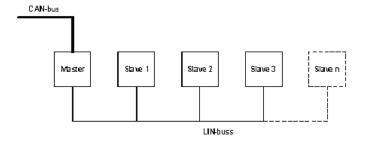

| Figure 3.8: LIN bus with single master node and 'n' slave nodes                      | 19  |

| Figure 3.9: LIN communication                                                        | 20  |

| Figure 3.10: MOST25 frame                                                            | 22  |

| Figure 3.11: MOST25 frame                                                            | 23  |

| FIGURE 3.12: TTP BUS TOPOLOGY                                                        | 24  |

| FIGURE 3.13: TTP COMMUNICATION CYCLE                                                 | 25  |

| Figure 3.14: FlexRay frame                                                           | 26  |

| FIGURE 3.15: FLEXRAY HYBRID TOPOLOGY                                                 | 26  |

| FIGURE 3.16: FLEXRAY BUS ACCESS                                                      | 27  |

| FIGURE 3.17: CYCLE MULTIPLEXING                                                      | 28  |

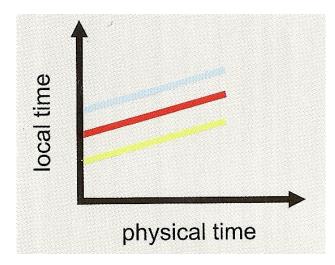

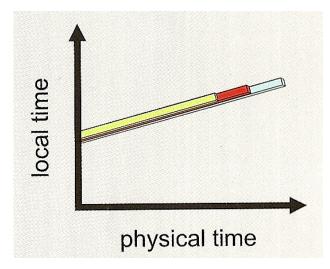

| Figure 3.18: Rate differences                                                        | 29  |

| Figure 3.19: Offset differences                                                      | 30  |

| FIGURE 3.20: RATE AND OFFSET CORRECTION APPLIED                                      | 30  |

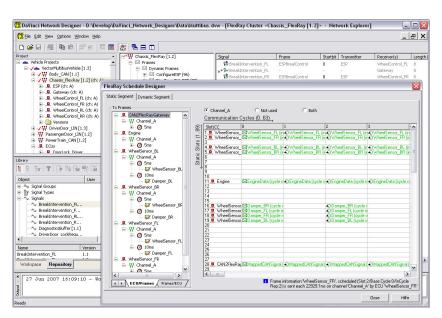

| FIGURE 3.21: DAVINCI FLEXRAY SCHEDULE DESIGN                                         | 32  |

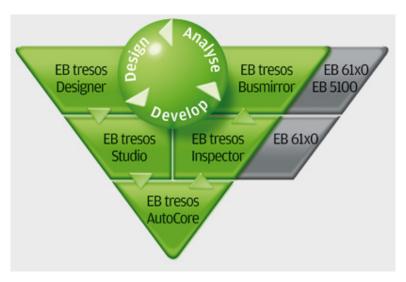

| FIGURE 3.22: EB TRESOS PRODUCT FAMILY                                                | 33  |

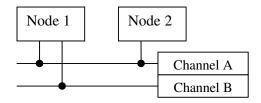

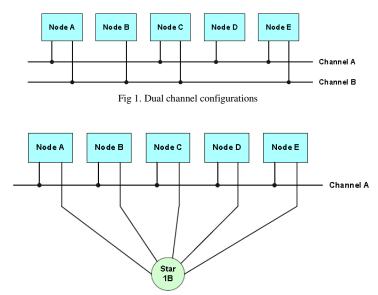

| Figure 4.1: A passive bus topology                                                   | 46  |

| Figure 4.2: Single channel hybrid network                                            | 46  |

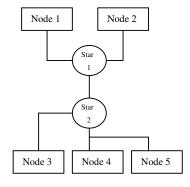

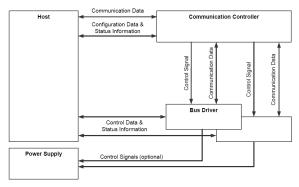

| FIGURE 4.3: LOGICAL INTERFACE                                                        | 47  |

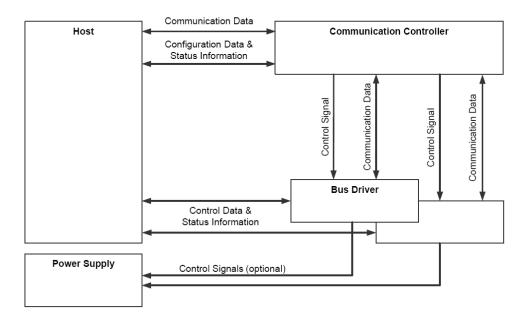

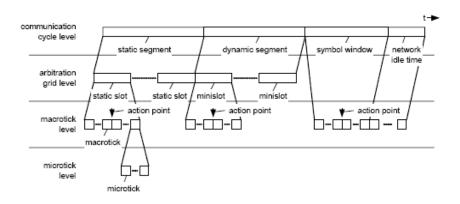

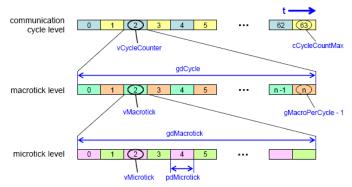

| FIGURE 4.4: TIMING HIERARCHY                                                         | 48  |

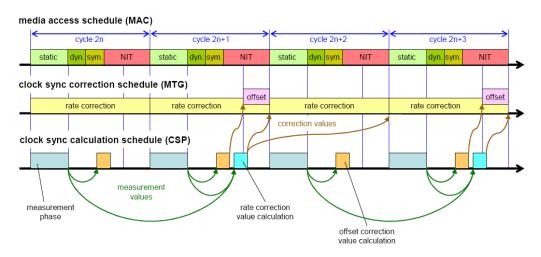

| FIGURE 4.5: THE RELATIONSHIP BETWEEN CLOCK SYNCHRONISATION AND THE MEDIA ACCESS TIME |     |

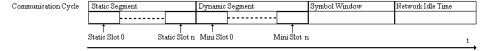

| Figure 4.6: Communication cycle                                                      |     |

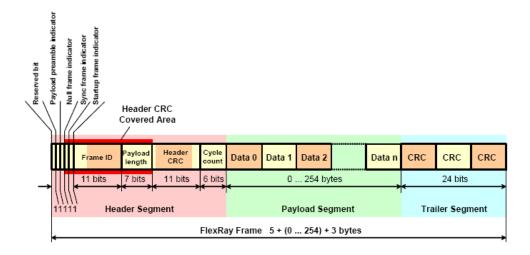

| Figure 4.7: Frame format                                                             | 53  |

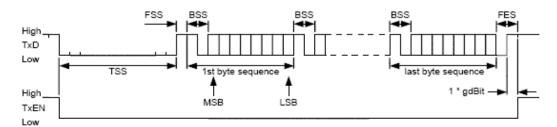

| Figure 4.8: Encoded bit stream                                                       | 56  |

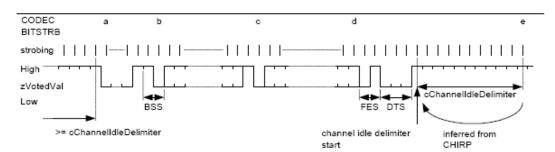

| Figure 4.9: Received bit stream                                                      | 58  |

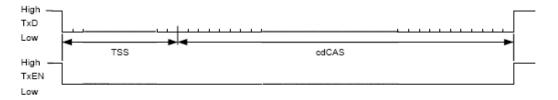

| FIGURE 4.10: CAS AND MTS ENCODING                                                    | 59  |

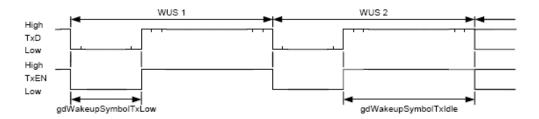

| FIGURE 4.11: WAKEUP PATTERN USING TWO WAKEUP SYMBOLS                                 | 60  |

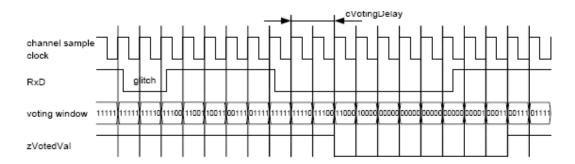

| FIGURE 4.12: SAMPLING AND MAJORITY VOTING OF A RECEIVED BIT PATTERN AT THE INPUT     | 62. |

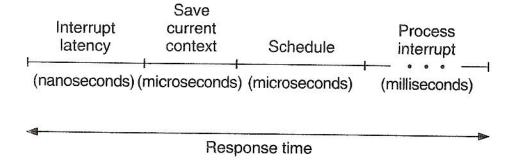

| FIGURE 5.1: INTERRUPT-DRIVEN RESPONSE TIME                                            | 68  |

|---------------------------------------------------------------------------------------|-----|

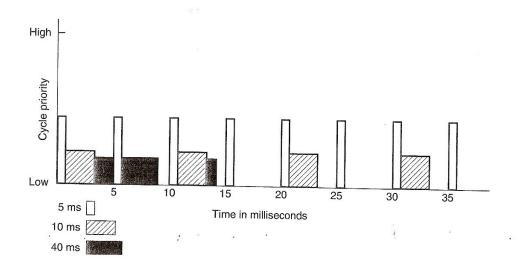

| FIGURE 5.2: TIMING CHART EXAMPLE                                                      | 70  |

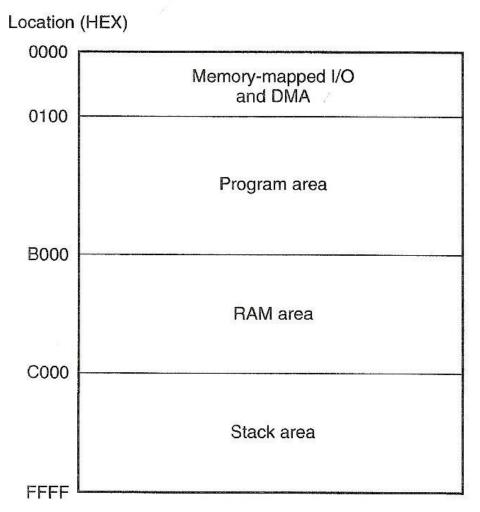

| FIGURE 5.3: STANDARD MEMORY MAP                                                       | 71  |

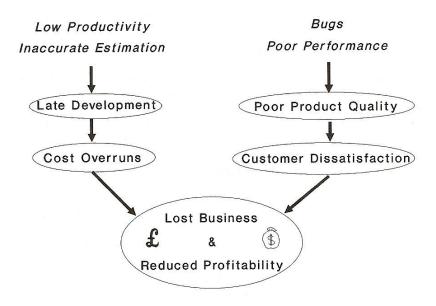

| FIGURE 5.4: THE EFFECT OF BAD SOFTWARE ON A COMPANY                                   | 75  |

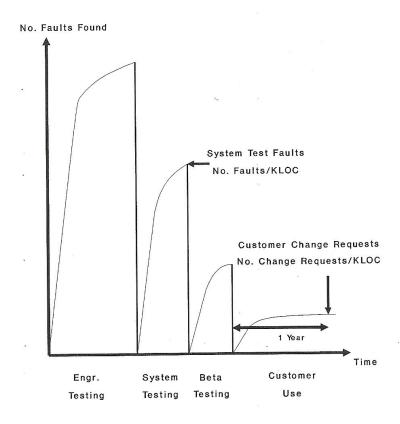

| FIGURE 5.5: NUMBER OF FAULTS FOUND IN SOFTWARE                                        | 76  |

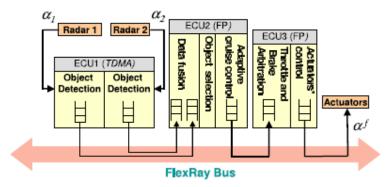

| FIGURE 5.6: FLEXRAY CONCEPTUAL ARCHITECTURE.                                          | 81  |

| FIGURE 5.7: SCHEDULED TRANSMISSION DEFINITION.                                        | 82  |

| FIGURE 5.8: FLEXRAY MODEL SYSTEM BASE                                                 | 84  |

| FIGURE 5.9: SYSTEM DEVELOPMENT PROCESS.                                               | 85  |

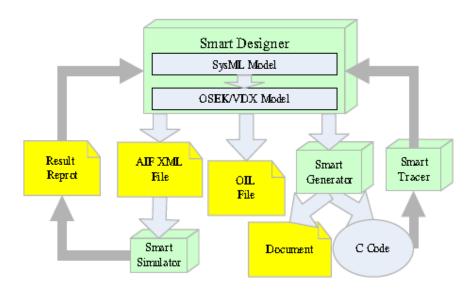

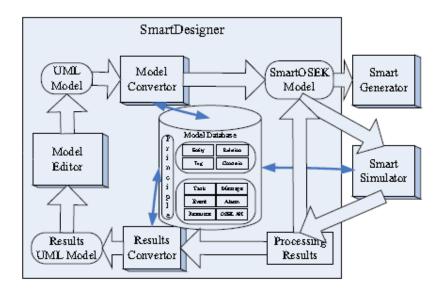

| FIGURE 5.10: THE SMART DESIGNER WORKFLOW                                              | 86  |

| FIGURE 5.11: THE SMART SIMULATOR ARCHITECTURE                                         | 87  |

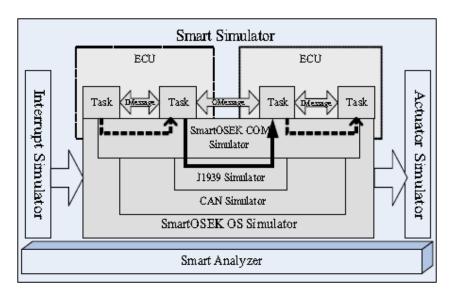

| FIGURE 5.12: SMARTOSEK ENGINE CONTROL SYSTEM                                          | 88  |

| FIGURE 5.13: EVENT STREAM WITH P=4 AND J=1                                            | 89  |

| FIGURE 5.14: SYMTAS DEVELOPED MODEL                                                   | 90  |

| FIGURE 5.15: SCHEDULING ALGORITHM                                                     | 91  |

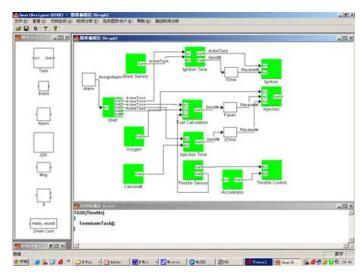

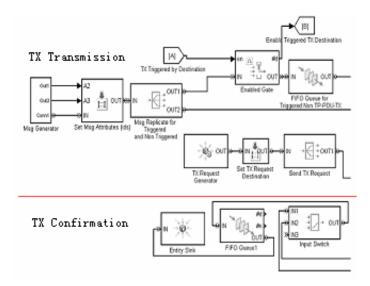

| FIGURE 5.16: NETWORK GATEWAY SIMULINK/SIMEVENTS MODEL                                 | 93  |

| FIGURE 5.17: AUTOMESH ARCHITECTURE                                                    | 94  |

| FIGURE 5.18: ABSTRACT DISTRIBUTED SYSTEM                                              | 96  |

| FIGURE 5.19: CO-SIMULATION MAPPED EXAMPLE.                                            | 96  |

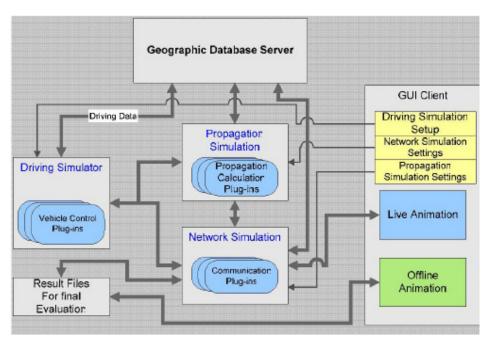

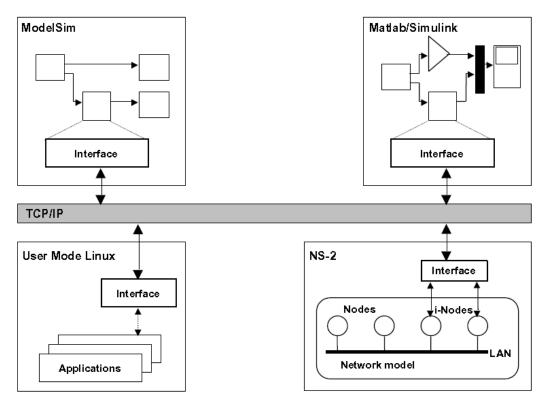

| FIGURE 5.20: SIMULATOR COMMUNICATION STRUCTURE                                        | 97  |

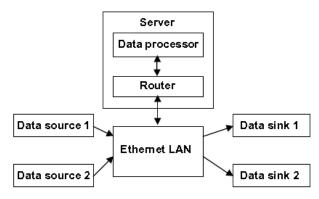

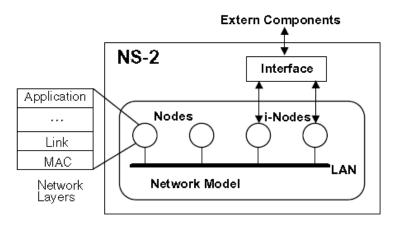

| FIGURE 5.21: NS-2 MODEL SHOWING THE INTERFACE MODULE                                  | 98  |

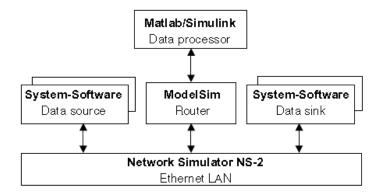

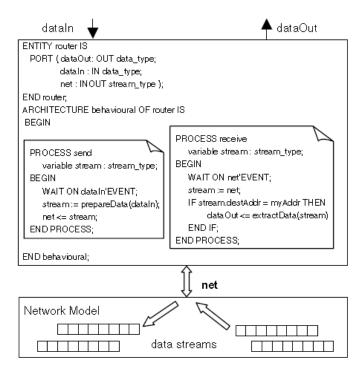

| FIGURE 5.22: ROUTER BLOCK MODEL                                                       | 99  |

|                                                                                       |     |

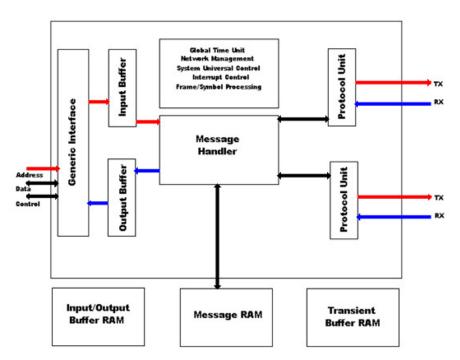

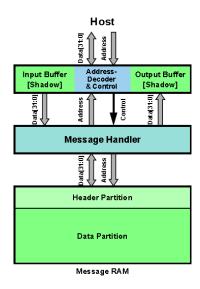

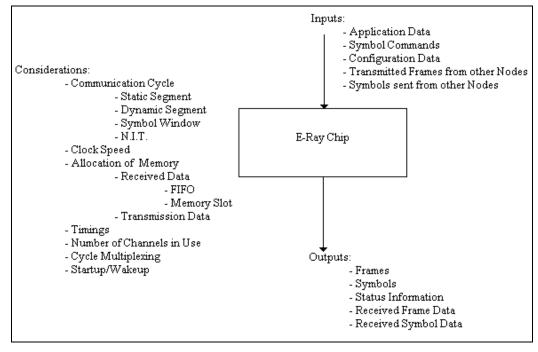

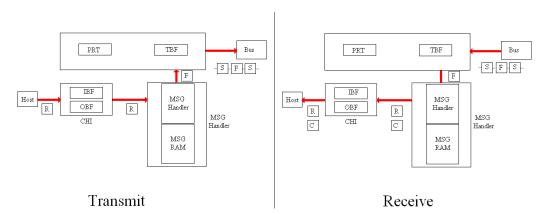

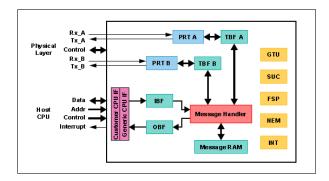

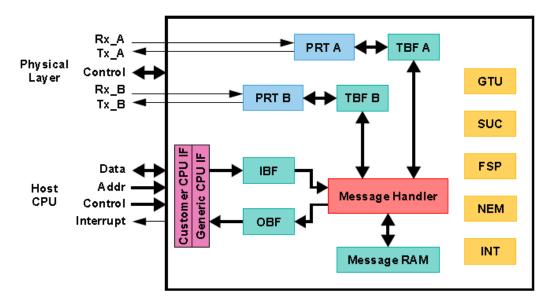

| FIGURE 6.1: BLOCK DIAGRAM OF THE WORKINGS OF AN E-RAY CHIP                            | 108 |

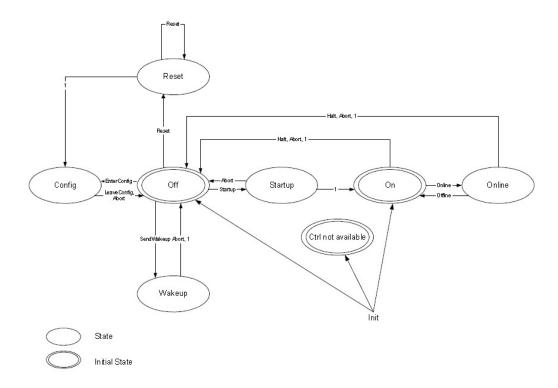

| FIGURE 6.2: POSSIBLE COMMUNICATIONS CONTROLLER STATES                                 | 112 |

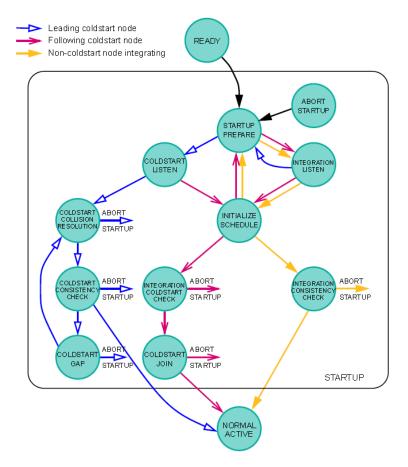

| FIGURE 6.3: STATE DIAGRAM FOR NODE ENTERING STARTUP                                   | 114 |

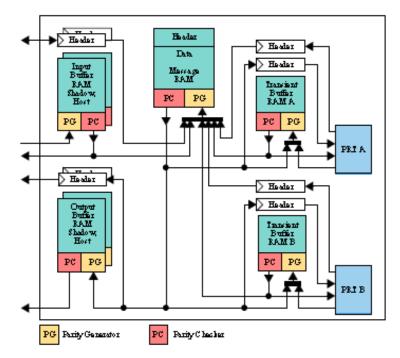

| FIGURE 6.4: RAM BLOCKS WITH LOCAL PARITY GENERATORS AND CHECKERS                      | 119 |

| FIGURE 6.5: HOST – MESSAGE RAM INTERFACE                                              | 121 |

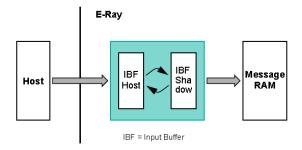

| FIGURE 6.6: DOUBLE BUFFER STRUCTURE INPUT                                             | 122 |

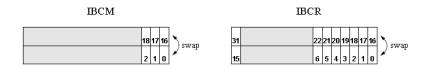

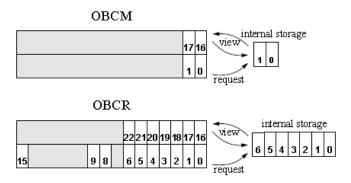

| FIGURE~6.7:~SWAPPING~INPUT~BUFFER~COMMAND~MASK~&~INPUT~BUFFER~COMMAND~REGISTER~BITS   | 122 |

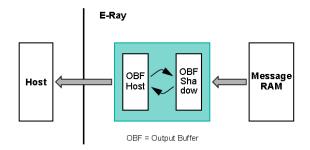

| FIGURE 6.8: DOUBLE BUFFER STRUCTURE OUTPUT                                            | 123 |

| Figure 6.9: Swapping output buffer command mask & output buffer command register bits | 123 |

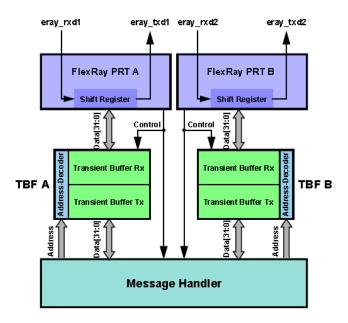

| FIGURE 6.10: TRANSIENT BUFFER RAMS                                                    | 124 |

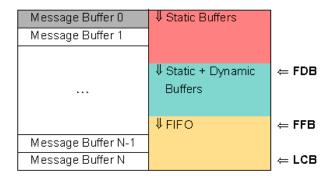

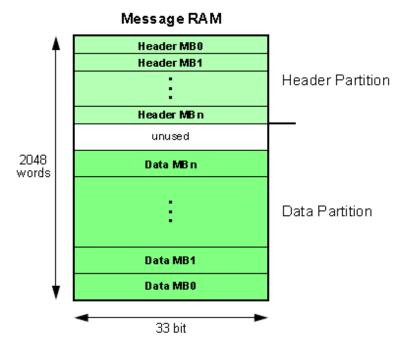

| FIGURE 6.11: MESSAGE RAM CONFIGURATION EXAMPLE                                        | 125 |

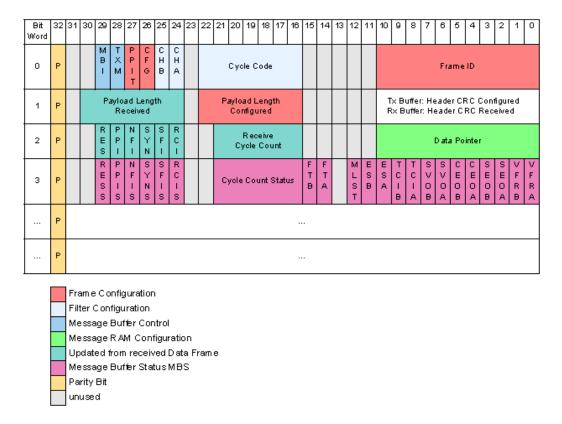

| FIGURE 6.12: HEADER SEGMENT IN MESSAGE RAM                                            | 126 |

| FIGURE 6.13: DATA PARTITION IN MESSAGE RAM EXAMPLE                                    | 128 |

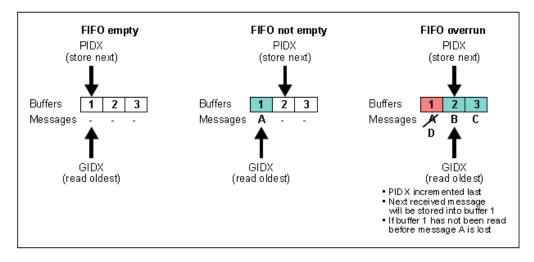

| FIGURE 6.14: EMPTY, NOT EMPTY AND OVERRUN STATES                                      | 132 |

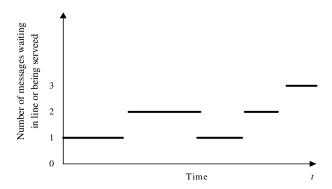

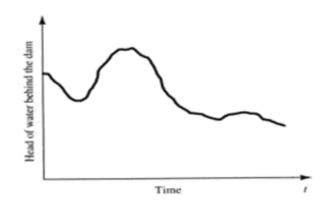

| FIGURE 7.1: DISCRETE-SYSTEM STATE VARIABLE                                            | 138 |

| FIGURE 7.2: CONTINUOUS-SYSTEM STATE VARIABLE                                          | 138 |

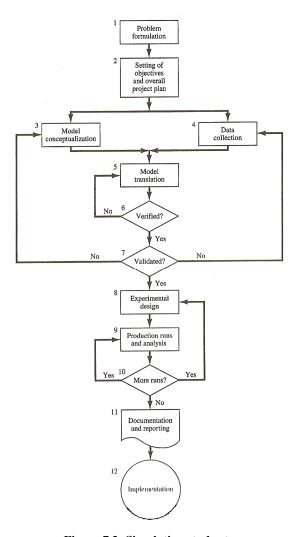

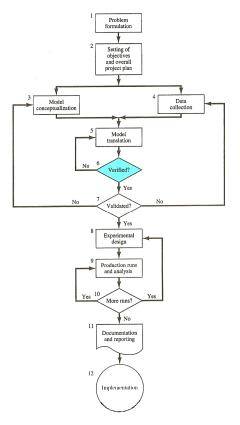

| FIGURE 7.3: SIMULATION STUDY STEPS                                        | 140 |

|---------------------------------------------------------------------------|-----|

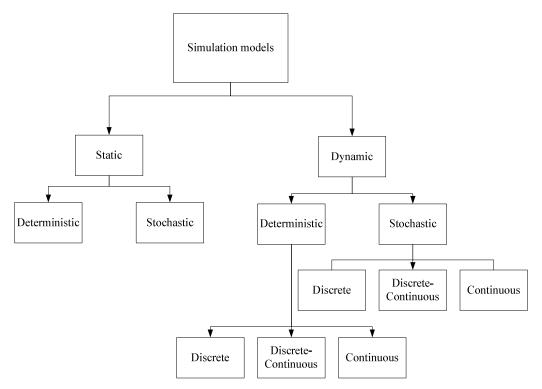

| FIGURE 7.4: SIMULATION MODELS                                             | 142 |

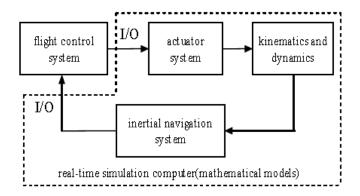

| FIGURE 7.5: FLIGHT CONTROL HILS SYSTEM                                    | 143 |

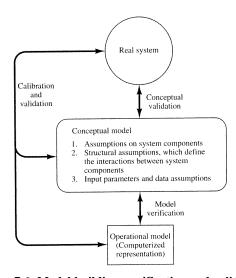

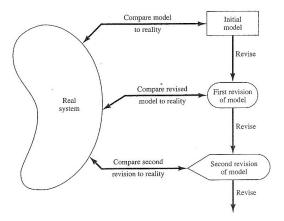

| FIGURE 7.6: MODEL BUILDING, VERIFICATION AND VALIDATION                   | 145 |

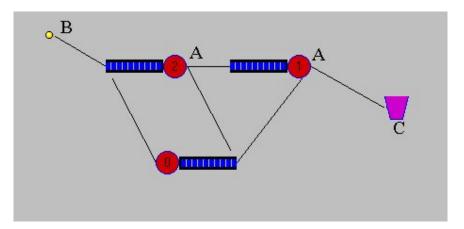

| FIGURE 7.7: OPEN QUEUING NETWORK                                          | 149 |

| FIGURE 7.8: CLOSED QUEUING NETWORK                                        | 149 |

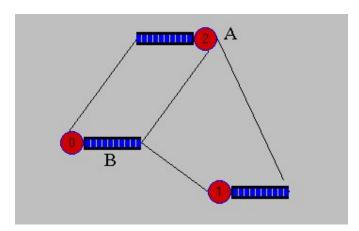

| FIGURE 7.9: MATHWORKS PRODUCT OVERVIEW                                    | 153 |

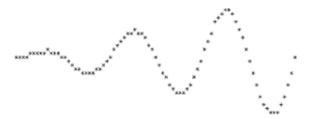

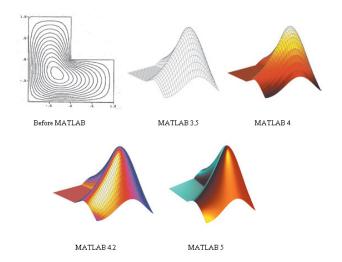

| FIGURE 7.10: FIRST MATLAB GRAPHICS                                        | 154 |

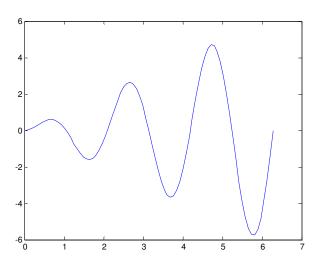

| FIGURE 7.11: MODERN MATLAB GRAPH                                          | 154 |

| FIGURE 7.12: MATLAB GRAPHICAL DEVELOPMENT                                 | 155 |

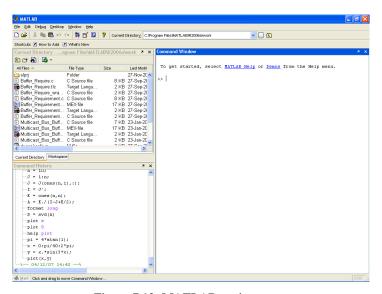

| FIGURE 7.13: MATLAB ENVIRONMENT                                           | 155 |

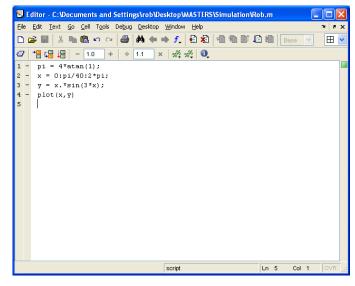

| Figure 7.14: An m-file                                                    | 156 |

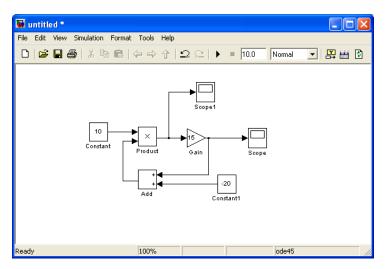

| FIGURE 7.15: SIMULINK ENVIRONMENT                                         | 157 |

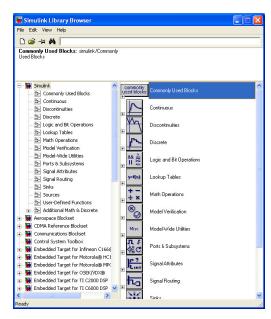

| FIGURE 7.16: SIMULINK LIBRARY                                             | 157 |

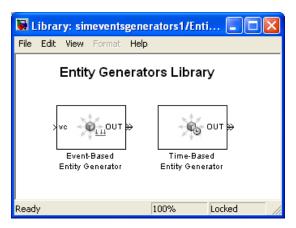

| FIGURE 7.17: SIMEVENTS LIBRARY WINDOW                                     | 158 |

| FIGURE 7.18: SIMEVENTS ENTITY GENERATOR OBJECTS                           | 159 |

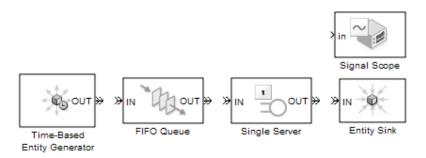

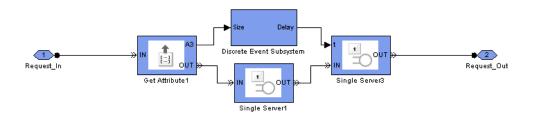

| FIGURE 7.19: SIMEVENTS TUTORIAL BLOCKS                                    | 160 |

| FIGURE 7.20: SINGLE SERVER PARAMETERS BOX                                 | 161 |

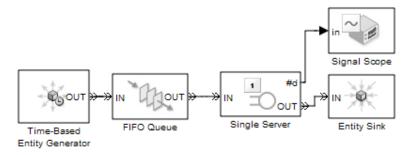

| FIGURE 7.21: TUTORIAL BLOCKS CONNECTED                                    | 161 |

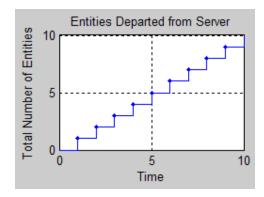

| FIGURE 7.22: TUTORIAL RESULTS                                             | 162 |

|                                                                           |     |

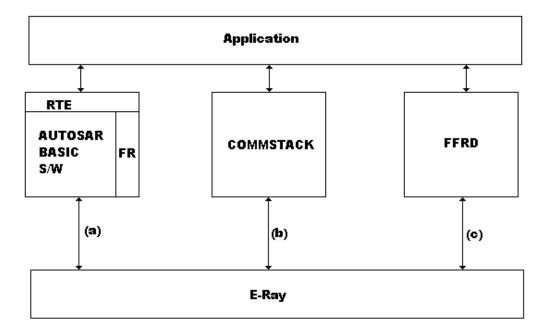

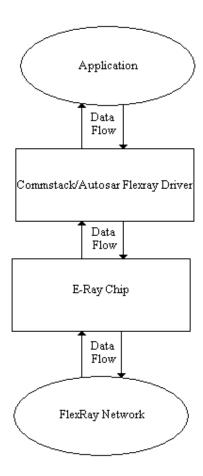

| FIGURE 8.1: FLEXRAY SOFTWARE DRIVER OPTIONS                               | 171 |

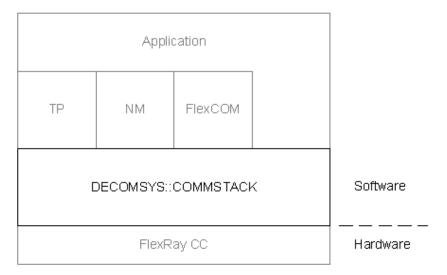

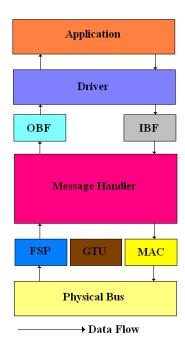

| FIGURE 8.2: COMMSTACK SYSTEM OVERVIEW                                     | 172 |

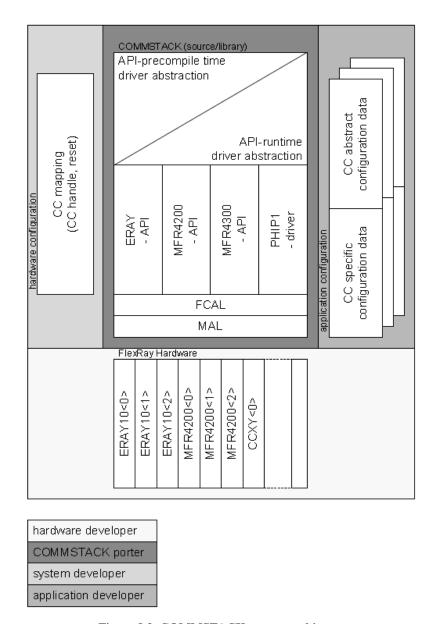

| FIGURE 8.3: COMMSTACK SYSTEM ARCHITECTURE                                 | 173 |

| FIGURE 8.4: COMMSTACK STATE DIAGRAM                                       | 174 |

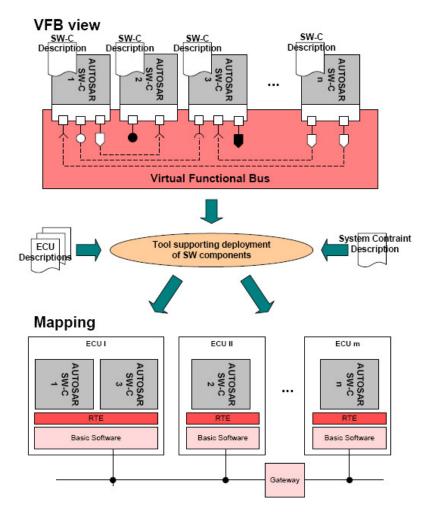

| FIGURE 8.5: VIRTUAL FUNCTIONAL BUS CONCEPT                                | 176 |

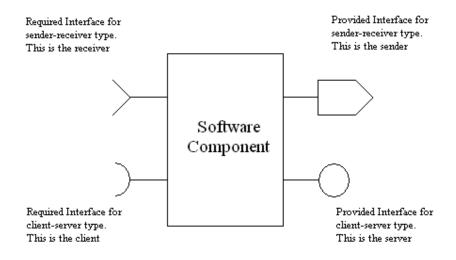

| FIGURE 8.6: SOFTWARE COMPONENT COMMUNICATION INTERFACE TYPES              | 177 |

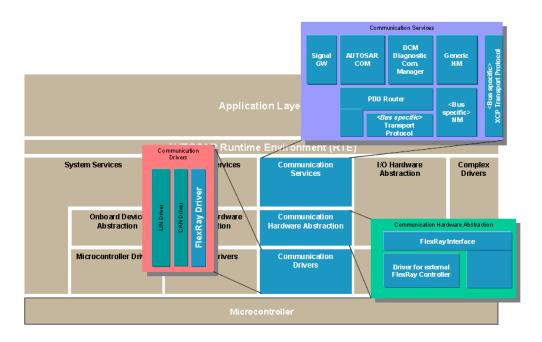

| FIGURE 8.7: FLEXRAY STACK LAYOUT                                          | 178 |

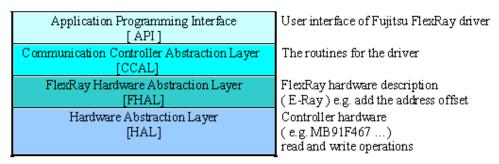

| FIGURE 8.8: FUJITSU FLEXRAY DRIVER LAYERS                                 | 180 |

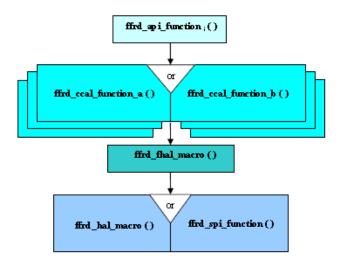

| FIGURE 8.9: FUJITSU FLEXRAY DRIVER ARCHITECTURE                           | 180 |

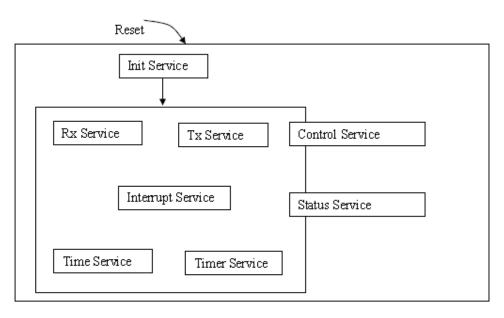

| FIGURE 8.10: FUJITSU FLEXRAY DRIVER SERVICES                              | 181 |

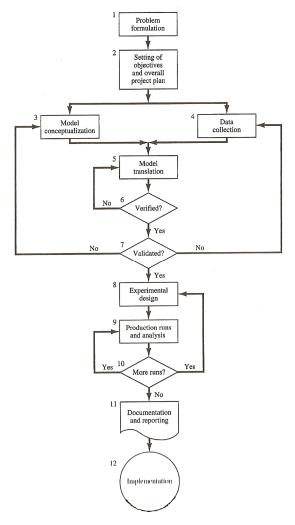

| FIGURE 10.1: SIMULATION STUDY STEPS                                       | 189 |

|                                                                           |     |

| FIGURE 11.1: FLEXRAY DEVELOPMENT STEPS                                    | 196 |

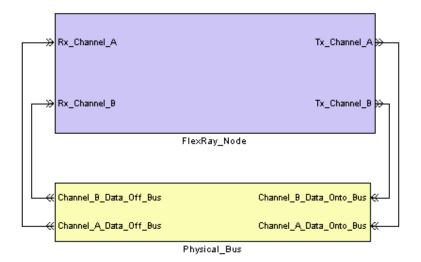

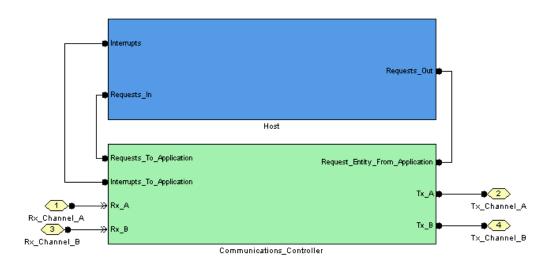

| FIGURE 11.2: FLEXRAY NODE ELEMENTS                                        | 197 |

| FIGURE 11.3: APPLICATION INPUTS, OUTPUTS AND CONSIDERATIONS               | 198 |

| FIGURE 11.4: SOFTWARE DRIVER INPUTS, OUTPUTS AND CONSIDERATIONS           | 199 |

| FIGURE 11.5: COMMUNICATIONS CONTROLLER INPUTS, OUTPUTS AND CONSIDERATIONS | 199 |

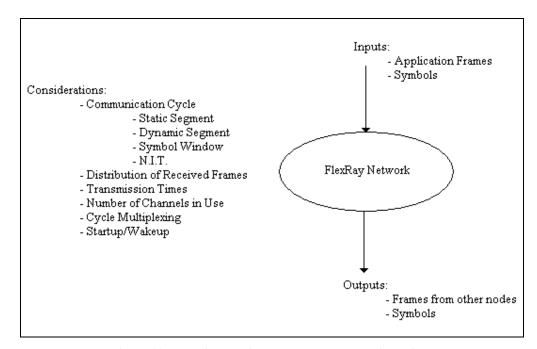

| FIGURE 11.6: PHYSICAL BUS INPUTS, OUTPUTS AND CONSIDERATIONS              | 200 |

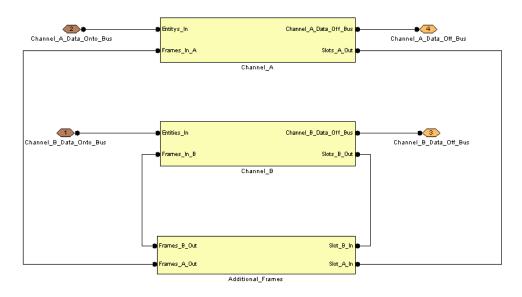

| FIGURE 11.7: TOP LAYER OF SIMULATION MODEL              | 201 |

|---------------------------------------------------------|-----|

| FIGURE 11.8: FLEXRAY MODEL SUBSECTIONS                  | 201 |

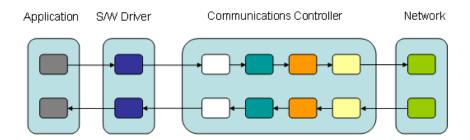

| Figure 11.9: Entity Paths                               | 202 |

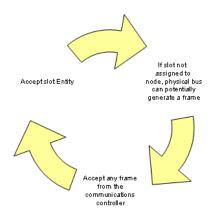

| FIGURE 11.10: SLOT ENTITY PATHS.                        | 204 |

| FIGURE 11.11: REQUEST ENTITY PATHS                      | 204 |

| FIGURE 11.12: FRAME ENTITY PATHS.                       | 205 |

| FIGURE 11.13: CYCLE ENTITY PATHS                        | 205 |

| FIGURE 11.14: MODEL AS A FLOW OF DATA                   | 207 |

| FIGURE 11.15: E-RAY DATA FLOW PATH                      | 208 |

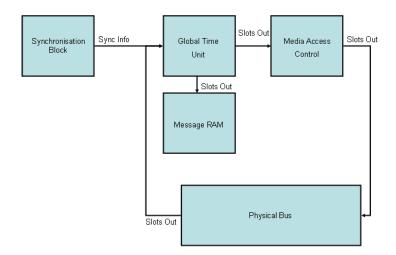

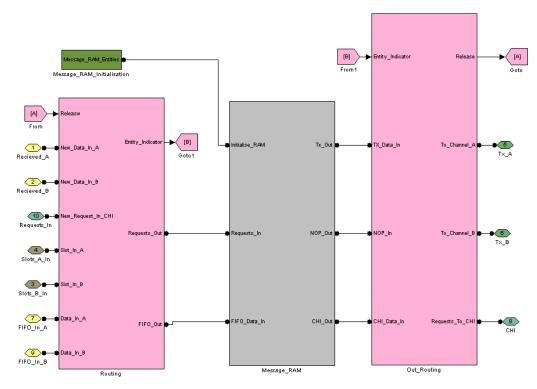

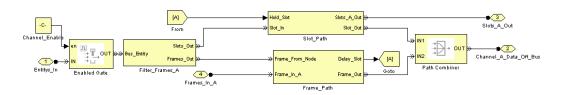

| FIGURE 11.16: E-RAY BLOCK DIAGRAM                       | 213 |

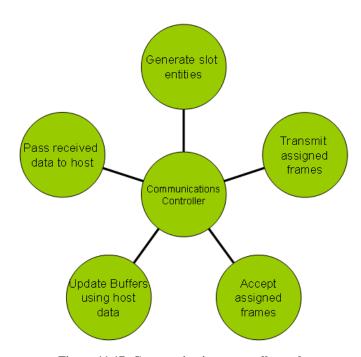

| FIGURE 11.17: COMMUNICATIONS CONTROLLER TASKS           | 213 |

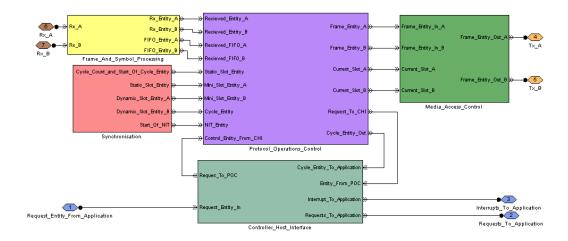

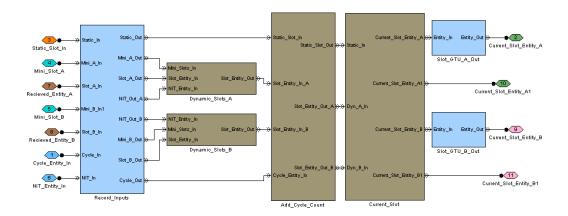

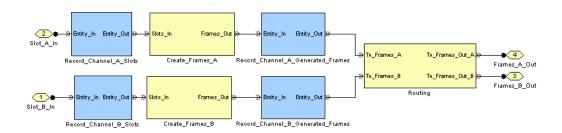

| FIGURE 11.18: MODEL OF THE COMMUNICATIONS CONTROLLER    | 214 |

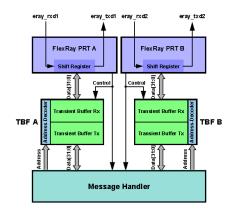

| FIGURE 11.19 TRANSIENT BUFFER RAM STRUCTURE             | 215 |

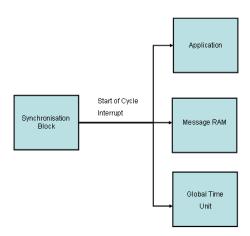

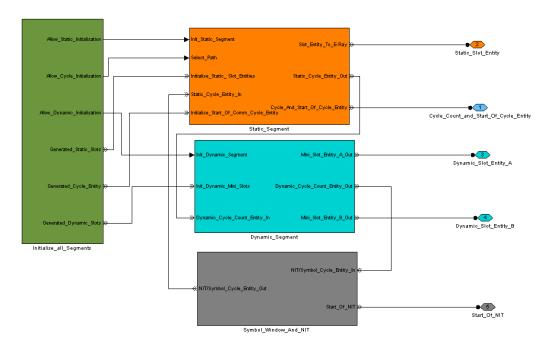

| FIGURE 11.20: SYNCHRONISATION BLOCK                     | 216 |

| FIGURE 11.21: CYCLE ENTITY FLOW DIAGRAM                 | 217 |

| FIGURE 11.22: INITIALISATION BLOCK                      | 218 |

| FIGURE 11.23: INITIALISE STATIC SEGMENT BLOCK           | 218 |

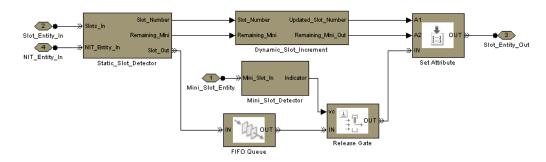

| FIGURE 11.24: STATIC SEGMENT BLOCK                      | 220 |

| FIGURE 11.25: GET START OF CYCLE                        | 220 |

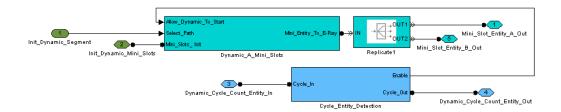

| FIGURE 11.26: DYNAMIC SEGMENT BLOCK                     | 221 |

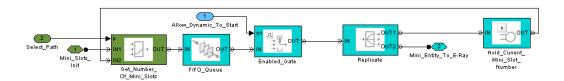

| FIGURE 11.27: DYNAMIC CHANNEL BLOCK                     | 221 |

| FIGURE 11.28: DYNAMIC ENABLE BLOCK                      | 221 |

| FIGURE 11.29: NETWORK IDLE TIME AND SYMBOL WINDOW BLOCK | 222 |

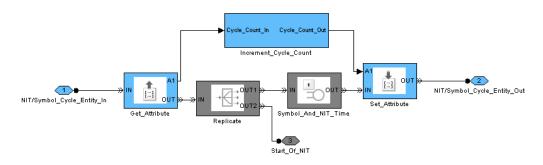

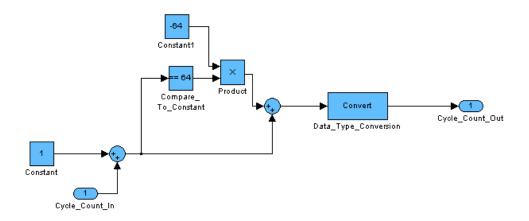

| FIGURE 11.30: INCREMENT CYCLE COUNT BLOCK               | 223 |

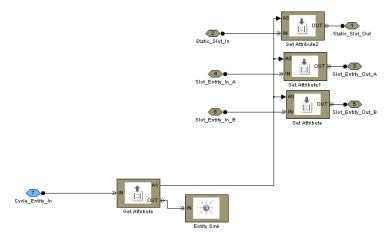

| FIGURE 11.31: GLOBAL TIME UNIT                          | 224 |

| FIGURE 11.32: CYCLE COUNT ATTRIBUTE ADDER               | 224 |

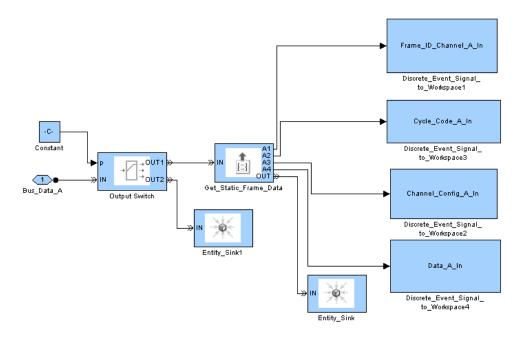

| FIGURE 11.33: DYNAMIC SLOT GENERATOR                    | 225 |

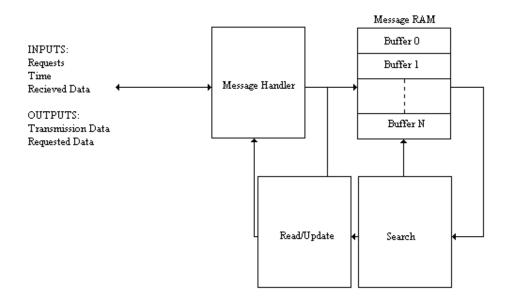

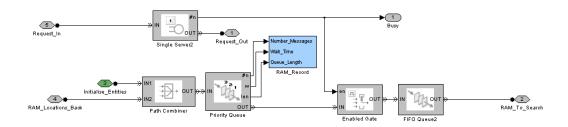

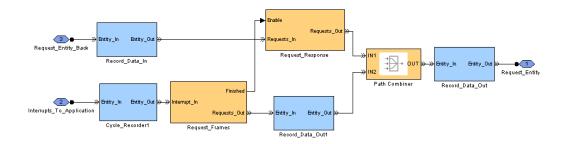

| FIGURE 11.34: MESSAGE HANDLER                           | 226 |

| FIGURE 11.35: MESSAGE RAM MODEL OPERATION               | 227 |

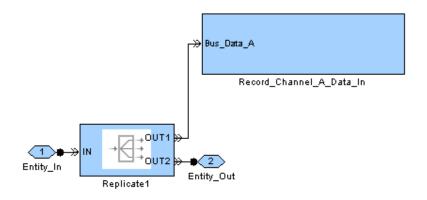

| FIGURE 11.36: MESSAGE RAM BUFFERS                       | 227 |

| FIGURE 11.37: MESSAGE HANDLER MODEL BLOCKS              | 228 |

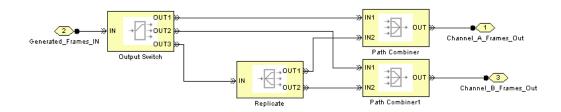

| FIGURE 11.38: OUTPUT BUFFER STRUCTURE                   | 229 |

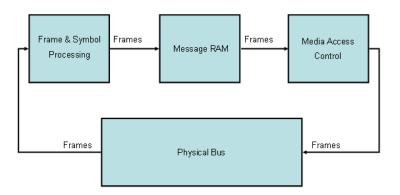

| FIGURE 11.39: PHYSICAL OPERATION DIAGRAM                | 230 |

| FIGURE 11.40: PHYSICAL BUS MODEL                        | 230 |

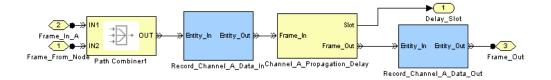

| FIGURE 11.41: CHANNEL 'X' LAYER                         | 231 |

| FIGURE 11.42: PROPAGATION DELAY CALCULATION BLOCKS      | 232 |

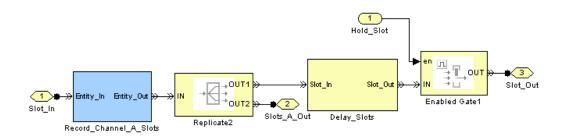

| FIGURE 11.43: DELAY SLOTS BLOCKS                        | 232 |

| FIGURE 11.44: ADDITIONAL FRAMES LAYER                   | 232 |

| FIGURE 11.45: FRAME ROUTING BLOCK                       | 233 |

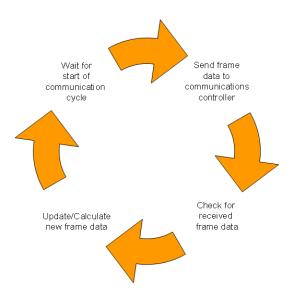

| FIGURE 11.46: APPLICATION LAYER OPERATION               | 234 |

| FIGURE 11.47: APPLICATION LAYER                                                  | 234 |

|----------------------------------------------------------------------------------|-----|

| FIGURE 11.48: DRIVER OPERATION.                                                  | 235 |

| FIGURE 11.49: SOFTWARE DRIVER LAYER                                              | 235 |

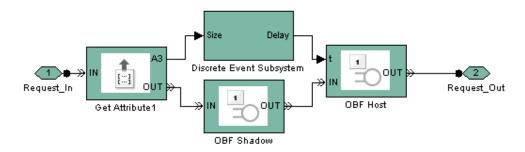

| FIGURE 11.50: SOFTWARE DRIVER DELAY                                              | 236 |

| FIGURE 11.51: BUS MONITOR MODEL                                                  | 237 |

| FIGURE 11.52: BUS MONITOR MODEL                                                  | 237 |

|                                                                                  |     |

| FIGURE 12.1: MODEL DEVELOPMENT FLOW CHART                                        |     |

| FIGURE 12.2: MODEL SUBSYSTEM BLOCK DIAGRAM                                       |     |

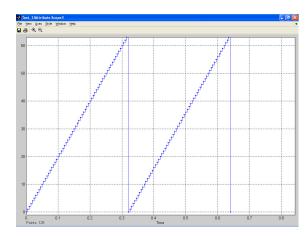

| FIGURE 12.3: SYNCHRONISATION TEST 1 ATTRIBUTE SCOPE GRAPH FOR CYCLE ENTITIES     | 246 |

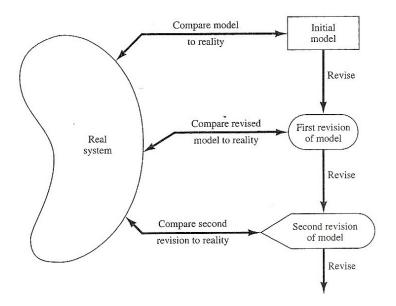

| FIGURE 13.1: CALIBRATION ITERATIVE PROCESS                                       | 262 |

| FIGURE 13.2: SIMULATION MODEL DEVELOPMENT PROCESS                                |     |

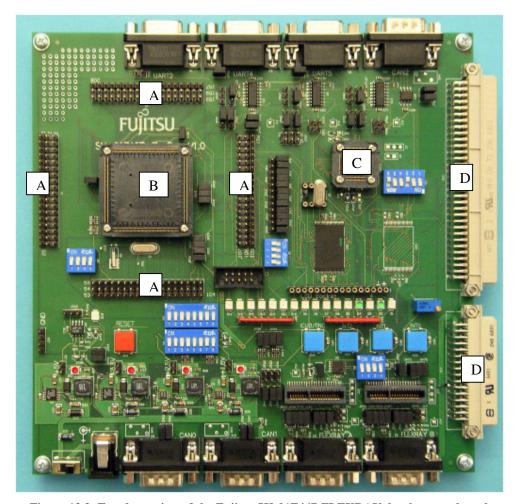

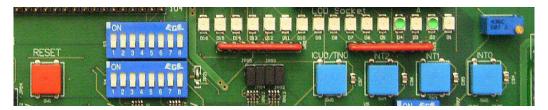

| FIGURE 13.3: TOP DOWN VIEW OF THE FUJITSU SK-91F467-FLEXRAY DEVELOPMENT BOARD    |     |

| FIGURE 13.4: FLEXTINY MODULE                                                     | 266 |

| FIGURE 13.5: PASSIVE STAR                                                        | 267 |

| FIGURE 13.6: VECTOR VN3600 USB INTERFACE FOR FLEXRAY                             | 267 |

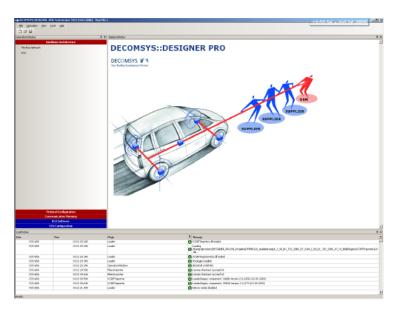

| FIGURE 13.7: DESIGNER PRO MAIN WINDOW                                            | 270 |

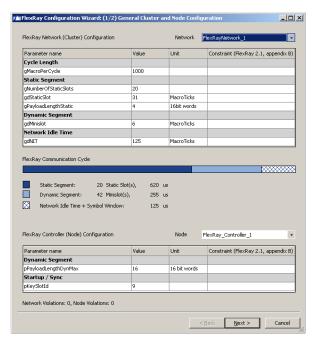

| FIGURE 13.8: THE FIRST PAGE OF THE FLEXRAY CONFIGURATION WIZARD                  | 271 |

| FIGURE 13.9: THE SECOND PAGE OF THE FLEXRAY CONFIGURATION WIZARD                 | 271 |

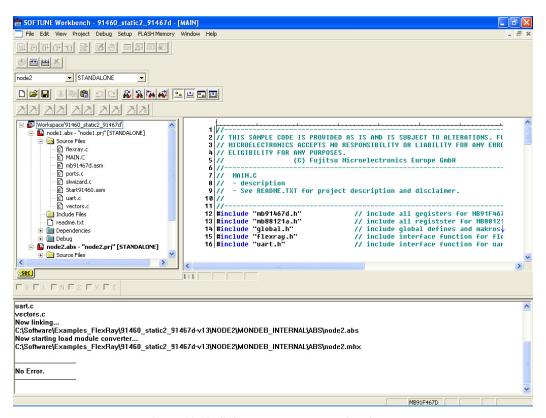

| FIGURE 13.10: SOFTUNE WORKBENCH MAIN WINDOW                                      | 272 |

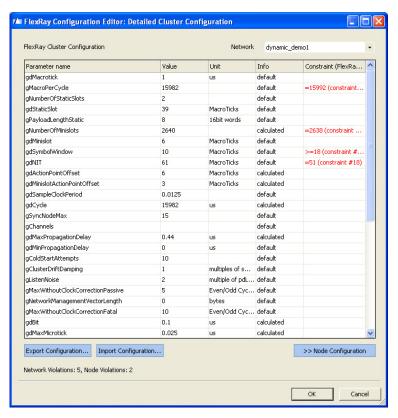

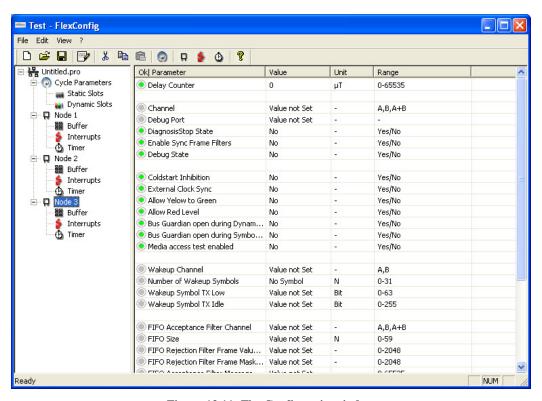

| FIGURE 13.11: FLEXCONFIG MAIN WINDOW                                             | 273 |

| FIGURE 13.12: CANALYZER.FLEXRAY TRACE WINDOW                                     | 274 |

| FIGURE 13.13: E-RAY STRUCTURE                                                    | 277 |

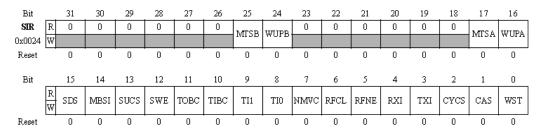

| FIGURE 13.14: E-RAY STATUS REGISTER INTERRUPTS                                   | 278 |

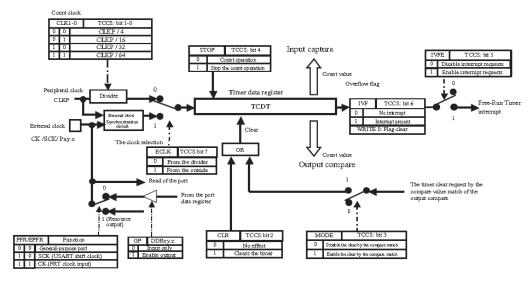

| FIGURE 13.15: FREE-RUN TIMER SETTINGS                                            | 280 |

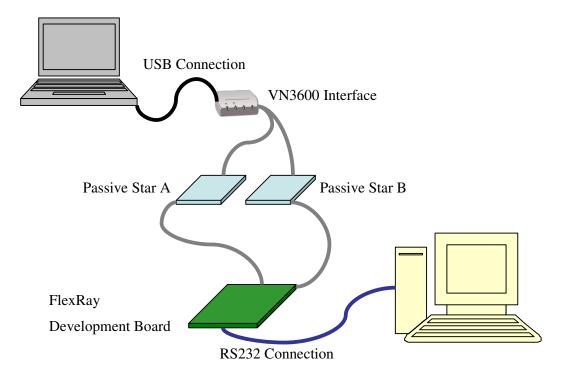

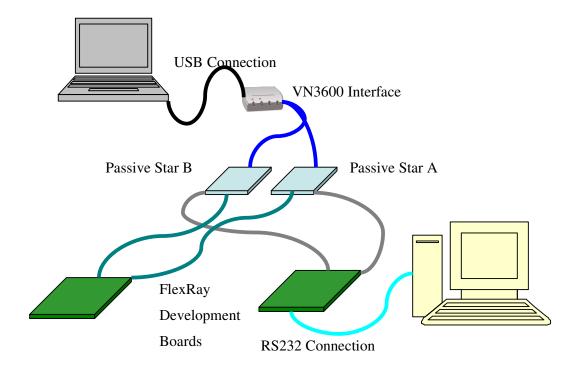

| FIGURE 13.16: CALIBRATION HARDWARE SETUP                                         | 281 |

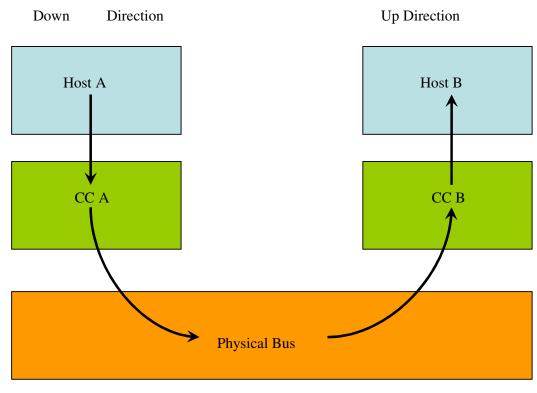

| FIGURE 13.17: FLOW DIRECTIONS OF DATA IN A FLEXRAY SYSTEM                        | 282 |

| FIGURE 13.18: FLOW DIRECTIONS OF DATA IN A FLEXRAY SYSTEM                        | 283 |

| FIGURE 13.19: CALIBRATION HARDWARE SETUP – REVISED                               | 288 |

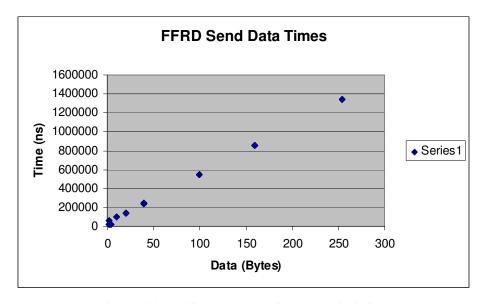

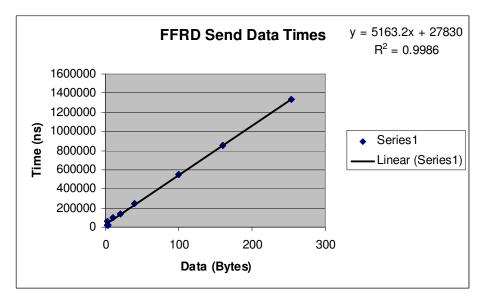

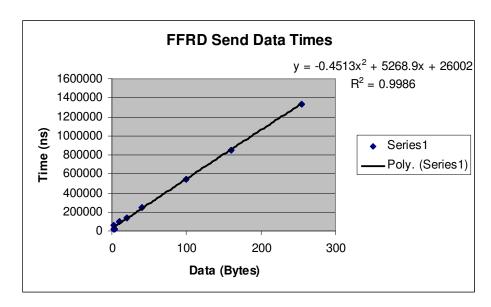

| FIGURE 13.20: FUJITSU FLEXRAY DRIVER TRANSMIT TIMINGS                            | 292 |

| FIGURE 13.21: FUJITSU FLEXRAY DRIVER TRANSMIT TIMINGS WITH LINEAR TREND LINE     | 292 |

| Figure 13.22: Fujitsu FlexRay Driver transmit timings with polynomial trend line | 293 |

| FIGURE 13.23: FUJITSU FLEXRAY DRIVER RECEIVE TIMINGS                             | 294 |

| FIGURE 13.24: FUJITSU FLEXRAY DRIVER RECEIVE TIMINGS WITH LINEAR TREND LINE      | 295 |

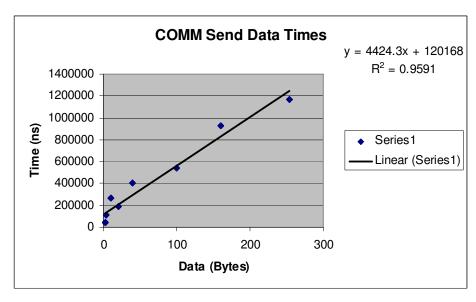

| FIGURE 13.25: COMMSTACK TRANSMIT TIMINGS                                         | 295 |

| FIGURE 13.26: COMMSTACK TRANSMIT TIMINGS WITH POLYNOMIAL TREND LINE              | 296 |

| FIGURE 13.27: COMMSTACK TRANSMIT TIMINGS WITH LINEAR TREND LINE                  | 296 |

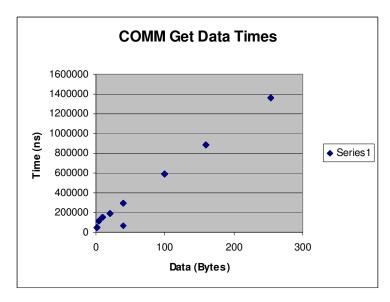

| FIGURE 13.28: COMMSTACK RECEIVE TIMINGS                                          | 297 |

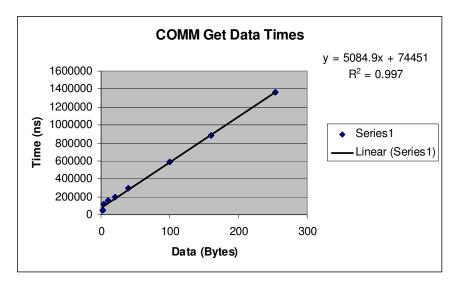

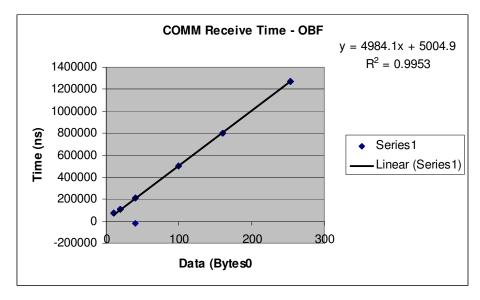

| FIGURE 13.29: COMMSTACK RECEIVE TIMINGS WITH LINEAR TREND LINE                   | 298 |

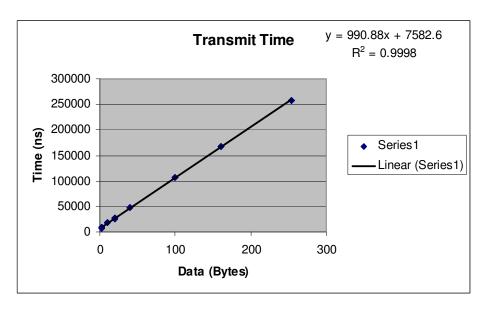

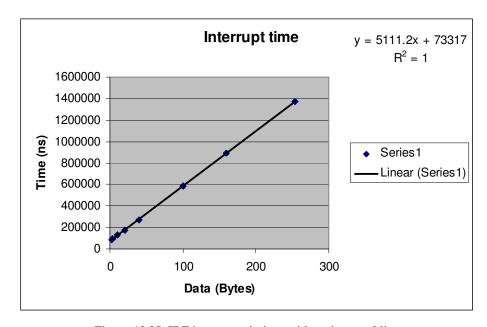

| FIGURE 13.30: TRANSMIT INTERRUPT TIMING WITH LINEAR TREND LINE    | 298 |

|-------------------------------------------------------------------|-----|

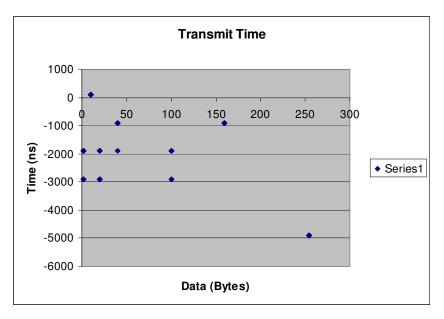

| FIGURE 13.31: TRANSMIT TIMES                                      | 299 |

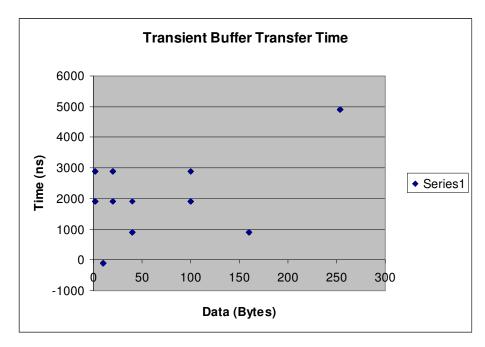

| FIGURE 13.32: TRANSIENT BUFFER TRANSFER TIMES                     | 300 |

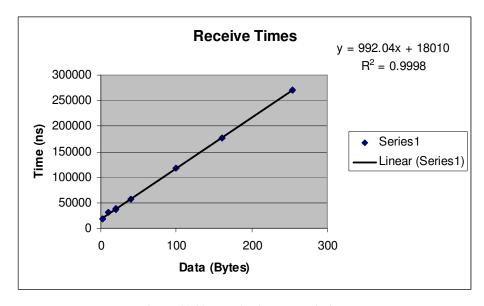

| FIGURE 13.33: RECEIVE INTERRUPT TIMINGS                           | 301 |

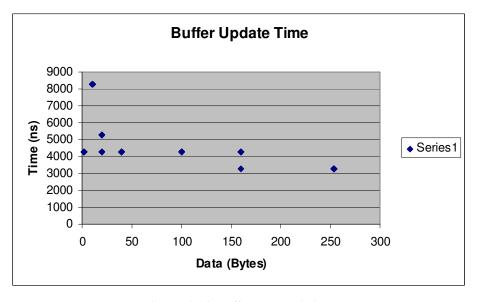

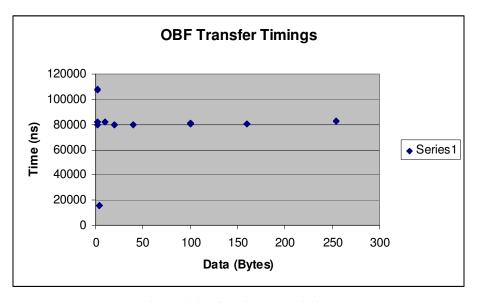

| FIGURE 13.34: BUFFER UPDATE TIMINGS                               | 301 |

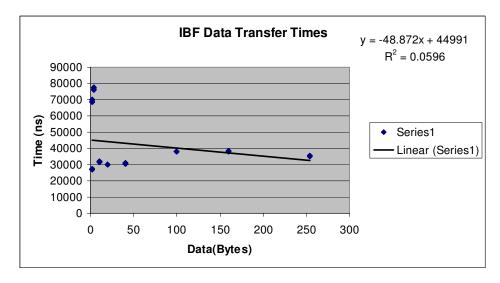

| FIGURE 13.35: IBF INTERRUPT TIMINGS WITH SERIES TREND LINE        | 303 |

| FIGURE 13.36: IBF TIMINGS WITH LINEAR TREND LINE                  | 303 |

| FIGURE 13.37: OBF INTERRUPT TIMINGS                               | 304 |

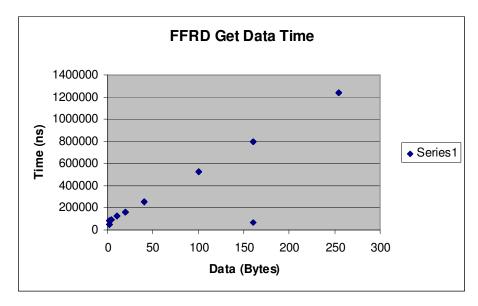

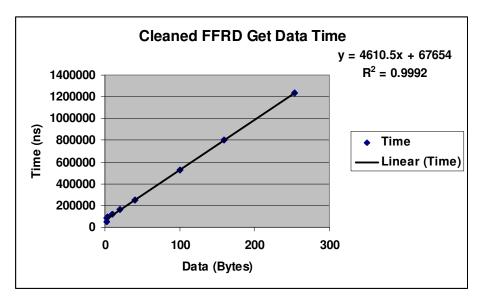

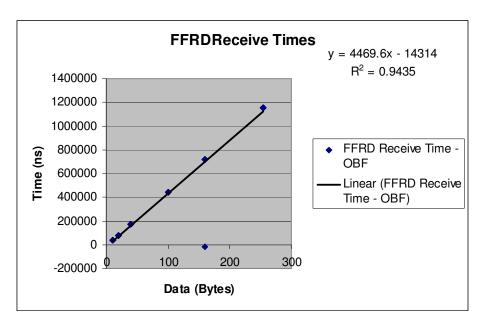

| FIGURE 13.38: FFRD AMENDED RECEIVE TIMINGS WITH LINEAR TREND LINE | 305 |

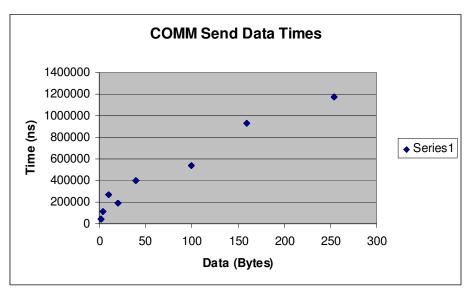

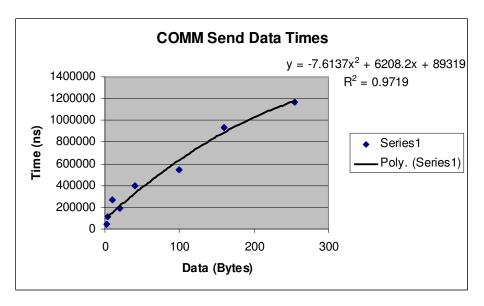

| FIGURE 13.39: COMMSTACK AMENDED TIMINGS WITH LINEAR TREND LINE    | 306 |

|                                                                   |     |

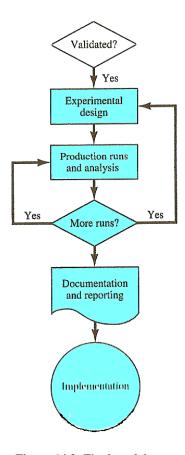

| FIGURE 14.1: MODEL BUILDING PROCESS                               | 324 |

| FIGURE 14.2: CALIBRATION ITERATIVE PROCESS                        | 325 |

| FIGURE 14.3: FINAL MODEL STEPS                                    | 345 |

#### TABLE OF TABLES

### **Table of Tables**

| TABLE 3.1: SAE AUTOMOTIVE NETWORK CLASSIFICATIONS          | 11  |

|------------------------------------------------------------|-----|

| Table 3.2: Event-triggered vs. time-triggered systems      | 14  |

| TABLE 3.3: MOST25 FRAME BYTE SUMMARY                       | 22  |

| TABLE 3.4: MOST25 FRAME BYTE SUMMARY                       | 23  |

| TABLE 4.1: K AS A FUNCTION OF A LIST OF VALUES             | 51  |

| TABLE 5.1: COMPONENTS OF SOFTWARE MEASUREMENT              | 78  |

| TABLE 5.2: FOCUS TYPE DEFINITIONS FOR FLEXRAY              | 82  |

| TABLE 5.3: SYSTEM ANALYSIS TECHNIQUE REQUIREMENTS SUMMARY  | 101 |

| Table 6.1: Message buffer assignment                       | 111 |

| Table 6.2: Error modes                                     | 117 |

| TABLE 6.3: MESSAGE RAM SCAN                                | 120 |

| TABLE 6.4: CYCLE SET DEFINITION                            | 130 |

| TABLE 6.5: EXAMPLES OF CYCLE SETS                          | 130 |

| TABLE 6.6: CHANNEL FILTERING BIT CONFIGURATIONS            | 131 |

| Table 7.1: Simulation software selection analysis          | 164 |

| Table 11.1: Entity attributes                              | 206 |

| TABLE 12.1: SYNCHRONISATION TEST 1 SIMULATION TIME RESULTS | 245 |

| TABLE 12.2: SYNCHRONISATION TEST 1 RESULTS SUMMARY         | 245 |

| TABLE 12.3: VERIFICATION TEST CASE PARAMETERS              | 250 |

| TABLE 12.4: VERIFICATION TEST CASE RANDOM NUMBER SEEDS     | 251 |

| TABLE 12.5: VERIFICATION TEST CASE 1 RESULT SUMMARY        | 252 |

| TABLE 12.6: VERIFICATION TEST CASE 2 RESULT SUMMARY        | 252 |

| TABLE 12.7: VERIFICATION TEST CASE 3 RESULT SUMMARY        | 253 |

| TABLE 12.8: VERIFICATION TEST CASE 4 RESULT SUMMARY        | 253 |

| TABLE 12.9: VERIFICATION TEST CASE 5 RESULT SUMMARY        | 253 |

| TABLE 12.10: VERIFICATION TEST CASE 6 RESULT SUMMARY       | 254 |

| TABLE 12.11: VERIFICATION TEST CASE 7 RESULT SUMMARY       | 254 |

| Table 12.12: Verification test case 8 result summary       | 254 |

| Table 12.13: Verification test case 9 result summary       | 255 |

| Table 12-14: Verification test case 10 result summary      | 255 |

#### TABLE OF TABLES

| TABLE 12.15: VERIFICATION TEST CASE 11 RESULT SUMMARY                 | 255 |

|-----------------------------------------------------------------------|-----|

| TABLE 12.16: VERIFICATION TEST CASE 12 RESULT SUMMARY                 | 256 |

| TABLE 12.17: VERIFICATION TEST CASE 13 RESULT SUMMARY                 | 256 |

| TABLE 12.18: VERIFICATION TEST CASE 14 RESULT SUMMARY                 | 256 |

| TABLE 12.19: SPEED TESTS                                              | 258 |

|                                                                       |     |

| TABLE 13.1: SK-91F467-FLEXRAY DEVELOPMENT BOARD INTERRUPT CONNECTIONS | 279 |

| TABLE 13.2: CALIBRATION TEST CASE PARAMETERS                          | 286 |

| TABLE 13.3: CALIBRATION TEST CASE RANDOM NUMBER SEEDS                 | 287 |

| Table 13.4: ffrd_api_get_time() time differences (µs)                 | 290 |

| TABLE 13.5: Free run timer differences (NS)                           | 290 |

| TABLE 13.6: INTERRUPT LATENCY TIMES (μS)                              | 291 |

| TABLE 13.7: TRANSMIT AVERAGES                                         | 300 |

| TABLE 13.8: RECEIVE AVERAGES.                                         | 302 |

| TABLE 13.9: IBF AVERAGES                                              | 304 |

| TABLE 13.10: OBF AVERAGES                                             | 305 |

| TABLE 13.11: SYSTEM TIMING CONSTRAINTS                                | 307 |

| TABLE 13.12: CALIBRATION TEST CASE 1 DATA                             | 309 |

| TABLE 13.13: CALIBRATION TEST CASE 2 DATA                             | 309 |

| TABLE 13.14: CALIBRATION TEST CASE 3 DATA                             | 310 |

| TABLE 13.15: CALIBRATION TEST CASE 4 DATA                             | 310 |

| TABLE 13.16: CALIBRATION TEST CASE 5 DATA                             | 311 |

| TABLE 13.17: CALIBRATION TEST CASE 1 ANALYSIS.                        | 312 |

| TABLE 13.18: CALIBRATION TEST CASE 2 ANALYSIS                         | 313 |

| TABLE 13.19: CALIBRATION TEST CASE 3 ANALYSIS                         | 314 |

| TABLE 13.20: CALIBRATION TEST CASE 4 ANALYSIS                         | 314 |

| TABLE 13.21: CALIBRATION TEST CASE 5 ANALYSIS                         | 315 |

| TABLE 13.22: CALIBRATION TEST RESULTS SUMMARY                         | 316 |

| TABLE 13.23: TRANSMIT PIPELINE TIMING                                 | 318 |

| TABLE 13.24: RECEIVE PIPELINE TIMING                                  | 319 |

|                                                                       |     |

| TABLE 14.1: VALIDATION TEST CASE PARAMETERS                           | 327 |

| TABLE 14.2: VALIDATION TEST CASE RANDOM NUMBER SEEDS                  | 328 |

| TABLE 14.3: VALIDATION TEST CASE 1 DATA                               | 329 |

| TABLE 14.4: VALIDATION TEST CASE 2 DATA                               | 329 |

| TABLE 14.5: VALIDATION TEST CASE 3 DATA                               | 330 |

| TABLE 14.6: VALIDATION TEST CASE 4 DATA                               | 331 |

| TABLE 14.7: VALIDATION TEST CASE 5 DATA                               | 331 |

| TABLE 14.8: VALIDATION TEST CASE 6 DATA                               | 332 |

| TABLE 14.9: CALIBRATION TEST CASE 7 DATA                              | 333 |

#### TABLE OF TABLES

| TABLE 14.10: VALIDATION TEST CASE 8 DATA                                          | 333 |

|-----------------------------------------------------------------------------------|-----|

| TABLE 14.11: VALIDATION TEST RESULTS SUMMARY                                      | 334 |

| TABLE 14.12: TRANSMIT PIPELINE TIMING                                             | 336 |

| TABLE 14.13: RECEIVE PIPELINE TIMING                                              | 337 |

| TABLE 14.14: BUFFER UPDATE TIME                                                   | 339 |

| TABLE 14.15: BUFFER READ TIME                                                     | 340 |

| TABLE 14.16: TOTAL SOFTWARE DRIVER TIMES                                          | 342 |

| FIGURE 14.3: FINAL MODEL STEPS                                                    | 345 |

| TABLE A.1: MODEL COLOUR CODING  TABLE B.1: PHYSICAL BUS INPUT WORKSPACE VARIABLES |     |

| TABLE B.2: NODE INPUT WORKSPACE VARIABLES                                         |     |

| TABLE B.3: COMMUNICATIONS CONTROLLER INPUT WORKSPACE VARIABLES                    |     |

| TABLE B.4: PROTOCOL OPERATIONS CONTROL INPUT WORKSPACE VARIABLES                  |     |

| TABLE B.5: PHYSICAL BUS OUTPUT WORKSPACE VARIABLES                                | IX  |

| TABLE B.6: NODE OUTPUT WORKSPACE VARIABLES                                        | X   |

| TABLE B.7: COMMUNICATIONS CONTROLLER OUTPUT WORKSPACE VARIABLES                   | XII |

| TABLE B.8: PROTOCOL OPERATIONS CONTROL OUTPUT WORKSPACE VARIABLES                 | XIV |

| TABLE B.9: ENTITY ATTRIBUTES                                                      | XV  |

# Section I: Thesis Overview

### Chapter 1. Thesis Overview

#### 1.1 Problem Specification

The main aim of this project is to research the workings of a FlexRay node and to suggest a method to optimally configure that node within a network.

As FlexRay is a new network protocol there is a need to fully understand how best to configure the network. This is so the maximum use of the network with a minimum associated cost can be achieved. The optimisation should also be done as there are several other networking schemes, such as CAN, LIN and MOST. No one networking scheme is perfect for all applications, and more than one type of network may be needed to efficiently implement all the systems found within a car. Implementing any number of these at the same time could increase cost and ultimately lead to problems if the systems do not work well together.

FlexRay looks likely to become the networking scheme of choice for safety critical systems such as X-by-wire systems (Pop et. al. 2007, p51). It is therefore important to identify any problems or areas for improvement early on. This will lead to a wider range of applications being developed that could increase customer comfort and safety.

The building of a model will allow the testing of a node with various configurations in a faster and cheaper way then by experimentation on a real network. It is therefore necessary to understand how a FlexRay network operates and how a node interacts with the other nodes on a network in order to accurately obtain realistic data.

#### 1.2 Research Questions

The main goal of this research is to develop a method to optimise a FlexRay node for efficient and reliable communication.

#### THESIS OVERVIEW

This research leads to a number of key questions that are to be answered. These questions are as follows:

- What aspects of the FlexRay controller configuration most affects the performance and design of distributed vehicle applications?

- What guidelines should be used to configure the protocol stack for best application performance?

- What techniques can be used to optimise local buffer usage for specific vehicle applications using a fixed global network message schedule?

#### 1.3 Document Layout

The layout of this document is as follows:

- Chapter 1 Thesis Overview: This chapter covers the problem specification, solution requirements and research questions in relation to this research.

- Chapter 2 Literary Review Introduction: This chapter introduces the topics and criteria for discussion covered in the literary review section of this thesis.

- Chapter 3 Automotive Networks: This chapter covers the current state of automotive networking technology.

- Chapter 4 FlexRay: This chapter describes the FlexRay protocol.

- Chapter 5 Performance Analysis: This chapter describes methods to carry

out performance analysis. Different methods that have been used in the past are

also introduced.

- Chapter 6 E-Ray: This chapter covers the workings of the Bosch E-Ray communication controller.

#### THESIS OVERVIEW

- Chapter 7 Discrete Event Simulation: This chapter describes the discrete event simulation method of modeling systems. Different simulation software packages are introduced and evaluated. MATLAB, the simulation package that was ultimately chosen is covered in detail. The selection process for the simulation software is also discussed.

- Chapter 8 FlexRay Software Drivers: This chapter focuses on the different software drivers that are available to implement FlexRay systems.

- Chapter 9 Literary Review Summary: This chapter summaries the literary review and the available literature. It also discusses the need for further research in the area of automotive networks.

- **Chapter 10 Methodology:** This chapter covers the methodology used to carry out the research.

- Chapter 11 Simulation Model Development: This chapter documents the specification and implementation of FlexRay node simulation model.

- Chapter 12 Verification: This chapter discusses the steps used to verify the model.

- Chapter 13 Calibration: This chapter covers the calibration procedure for the model. Test cases are outlined and the calibration process is reviewed. The equipment that was used is outlined and test results are summarised.

- Chapter 14 Validation: This chapter covers the steps used to validate the simulation model. Test cases are outlined and the validation process is reviewed.

- Chapter 16 Conclusion: This chapter summarises the work done during the research, conclusions drawn from the results and suggestions for areas of further study are put forward.

#### 1.4 References

Pop, T., Pop, P, Eles, P. and Peng, Z. (2007) Bus Access Optimisation for FlexRay-Based Distributed Embedded Systems, Proceedings of the Conference on Design, Automation and Test in Europe, Nice, France, April 16-20 2007, IEEE Computer Society Washington, DC, 51 – 56.

# Section II: Literary Review

# Chapter 2 . Literary Review Introduction

#### 2.1 Scope

The literary review introduces key concepts and topics that were looked at to successfully complete the project. The information provided allows the reader to gain an understanding of why the research is necessary. It also allows the reader to form opinions on the methods that were chosen to complete the research. The background information provided also allows the reader to understand the significance of the research.

A number of topics are covered in this literary review. The main topics covered can be summarised as:

- The main aspect of the project involves improving the performance of a FlexRay node, therefore FlexRay and its alternatives are explored.

- The Bosch E-Ray chip is the FlexRay communications controller that was available for study to this project. Its key features and implementation are described.

- The method of adapting and running tests of a FlexRay node is simulation. The

reasons for this methodology to be chosen along with simulation theory are

covered.

- The current state of automotive networking and the need for research in this area are introduced.

- Analysis techniques to quantify the performance of the model are discussed.

#### 2.2 Terminology

This section outlines terminology that will be used in the following chapters. It is an alphabetical listing with brief definitions for each phrase. It should be noted that the definitions may not cover all terms that the reader is unfamiliar with. An attempt by the author has been made to give a brief explanation, within the scope of this thesis, of all the technical terms used that the reader may not be familiar with. If an explanation of a term is given elsewhere in this thesis it has been omitted from this section.

**Actuator:** A device that converts electrical signals into physical actions. An example of this is a D.C. motor which converts an electrical signal into a turning motion.

**Application:** A piece of software that defines how information is handled or processed by a computer system.

**Bus:** The physical wire or wires over which information is sent between two different nodes on a network (see the definition of a node given below).

**Channel:** This is a path through which information 'flows'. A FlexRay bus is an example of a channel.

**Communications Controller:** A computer chip specifically designed to transmit and receive data over a communications channel. For example, in the case of a FlexRay communications channel, data is handled according to the FlexRay protocol specifications.

**Host:** A microprocessor unit (MPU) that has a communications controller embedded or attached. An application on the host may send and/or receive data to/from the FlexRay bus. It may also process information in order to implement a task or function.

**Multiplexing:** This is a where one or more device share a common communication channel. It splits either the time or frequency spectrum available to allow the devices access to the channel.

**Node:** A piece of hardware that can consist of a communications controller and host MPU. There may also be attached a sensor and/or actuator. The host is attached to the communications channel via a communications controller. The application running on the node defines its function.

**Register:** A dedicated area of an electronic chip that stores values used to determine the working of the device or program.

**Sensor:** A sensor reads in information from a physical device and converts it into an electrical value. An example of this is a thermistor that converts temperature into an analogue or digital signal that can be displayed on a dash board display.

**X-by-wire:** A method of replacing physical mechanical links with computer-assisted actuators.

#### 2.3 Criteria for Discussion

Each chapter was included under one of the following criteria:

- 1. It provides necessary information to understand the need of the project.

- 2. It provides necessary information to understand the methods used to carry out the project.

- 3. It gives an understanding of the equipment and methodologies available to successfully carry out the project.

#### 2.4 Limits of the Review

The literary review covers many topics. However there are a number of areas related to FlexRay that have not been covered. An attempt has been made to only include the necessary information to allow the reader to understand the need for the research.

## Chapter 3 . Automotive Networks

#### 3.1 Introduction

There are a number of different communication protocols that have been developed for use by the automotive industry. Each networking scheme is intended for a different purpose. This chapter introduces various networking protocols used in the automotive industry. It also attempts to outline the challenges faced by automotive networks and highlight any weaknesses in relation to the available networks.

#### 3.2 Automotive Networks

Since the first electronic device was installed in an automotive vehicle the number of components has increased dramatically. It is estimated that up to 90% of innovations in the automotive industry are due to electric and electronic systems (Fennel 2006). This is set to increase further with new applications such as x-by-wire applications.

Figure 3.1 (TechInsights 2008) shows how the increase in the number computer components leads to an exponential increase of the number of connections needed to connect each device. Without employing a serial communications network to connect each ECU the increased number of wires would become impractical. Each of the communications networks described in this chapter uses serial transmission over a small number of wires. This allows all the nodes on the network to be connected while reducing the number of individual point-to-point connections.

##

Figure 3.1: Computer components and possible connections

Navet et. al. (2005) describes how in 1994 the Society for Automotive Engineers (SAE) defined a classification for automotive networks. Every automotive networking protocol belongs to one of the SAE classes of automotive networks. Table 3.1 details the classifications.

| Class | Functions                               | Bit Rate          | Example Protocols    |

|-------|-----------------------------------------|-------------------|----------------------|

| A     | Simple, low-cost, control applications. | <10kb/s           | LIN, TTP/A           |

| В     | Inter-ECU communication applications    | 10 – 125 kb/s     | J1850, low-speed CAN |

| С     | Powertrain/chassis applications         | 125 kb/s – 1 Mb/s | High-speed CAN       |

| D*    | Multimedia applications, X-by-wire,     | > 1 Mb/s          | MOST, TTP/C, FlexRay |

|       | Fault tolerant applications             |                   |                      |

Table 3.1: SAE automotive network classifications

Usually the higher the classification of a particular networking protocol, the more complex it becomes. This complexity comes with advantages and drawbacks. For instance FlexRay is more complex than LIN; however FlexRay provides a higher bit rate and the ability to transmit data in both a time-triggered and event-triggered manner. This will increase the cost in terms of setup time and the actual cost of components while providing greater data throughput.

<sup>\*</sup> Class D is not formally defined. However it is considered to be networks operating over 1Mb/s (Navet et. al. 2005).

#### 3.3 Networking Type Overview

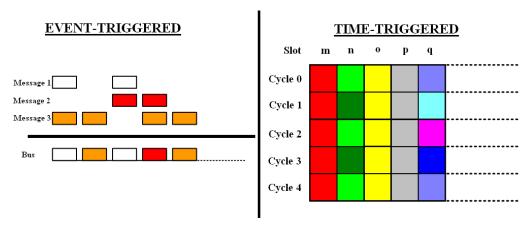

Each of the protocols described in this chapter can be classified as either an event-triggered or time-triggered system. A time-triggered network sends messages at fixed points in time. Event-triggered systems send messages in reaction to stimuli. For instance if a person wishes to open a window in a car they might press a button. This event will then generate a message to operate a motor to control the window. This section highlights some problems and benefits of both types of system.

Event-triggered: Event-triggered messages have unpredictable transmission patterns; this makes analysis of performance relatively difficult. However for sporadic transmission behavior this is a good implementation and leads to a flexible system (Kopetz 2000). A comparative study of time-triggered and event-triggered systems found that, during heavy bus loading, event-triggered messages may fail to transmit due to higher priority messages blocking lower priority messages. However when an average delay is taken of the messages sent, the event-triggered protocols experienced a shorter delay (Claesson et. al. 2003). This may be due to the fact that higher priority messages may not occur as frequently as lower priority events. From the point of view of resource utilisation this leads to event-triggered systems being superior but they do not scale as easily as time-triggered systems, this is due to a lack of any 'temporal firewall' (Kopetz 1991). A temporal firewall is a way to prevent unwanted communications between the different nodes on a network by the multiplexing of time slices to allow or deny communication.

**Time-triggered:** Time-triggered messages have predictable transmission patterns; this makes for easier performance analysis. Interoperability of the different nodes in the network is also an advantage achieved from employing this method as each node is given a specific time slot to transmit. Time-triggered systems are also ideal for real-time systems where deadlines must be met (Kopetz 2000). The design stage of a time-triggered system can be more complicated compared to a similar system implemented as an event-triggered system. This is because timing constraints must be met to ensure information is sent out before a deadline. This leads to a more detailed planning phase where timing constraints of all aspects of a system should be considered. It is necessary that an application running on a particular node transmits any data to any interested nodes within a given time. This design stage will however lead to a reduced verification time of the time-triggered system (Kopetz 1991).

**Event-triggered vs. Time-triggered:** Scheler and Schröder-Preikschat (2006) compare event-triggered and time-triggered architecture. They looked at analysability, predictability, testability, extensibility, fault-tolerance and resource utilisation. A summary of this breakdown can be seen in Table 3.2. It can be concluded from their findings that neither approach is sufficient for every system. If the data is sporadic then event-triggered protocols will be a good approach under low bus loadings. However if the system is a real-time system and must adhere to strict timing constraints, then time-triggered protocols should be used. However the development process may be longer in this case.

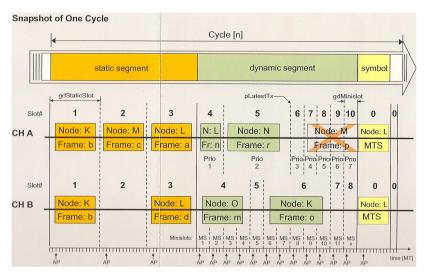

Figure 3.2 shows the traffic patterns for event-triggered and time-triggered systems. In event-triggered system messages may attempt to gain access to the communications bus at the same time. The message with the highest priority will gain access to the bus. Other messages must then wait until the communications bus is free before again attempting to gain access to the bus. In a time-triggered system a message is assigned to a slot at the design time. In Figure 3.2 Message 1 has the highest priority and message 3 the lowest Priority. The time-triggered messages are all represented by different colours. The slots may make use of a multiplexing technique to allow different messages to be transmitted during the same time slot but over different communications cycles. It can be seen that the same message is transmitted during the same time slot every communication cycle if multiplexing of the slots is not implemented. Multiplexing of slots must be set at design time also.

Figure 3.2: Event-triggered and time-triggered network patterns

|                 | Time-Triggered               | Event-Triggered              | Conclusion                |

|-----------------|------------------------------|------------------------------|---------------------------|

| Analysability   | Statistically computed       | Response time analysis       | Neither method provides   |

|                 | schedules are used to        | technique is used need to    | a better solution as      |

|                 | analyse the schedulability.  | analyse the schedulability.  | detailed knowledge is     |

|                 |                              |                              | necessary to perform the  |

|                 |                              |                              | analysis.                 |

| Predictability  | Easily analysed for          | Dynamic response to          | Time-triggered systems    |

|                 | predictability.              | events makes the system      | make analysis of          |

|                 |                              | less predictable. A system   | communication patterns    |

|                 |                              | may still be deterministic.  | easier as this is set at  |

|                 |                              |                              | design time.              |

| Testability     | Best to test for worst case  | Best to test for worst case  | Neither method is easier  |

|                 | performance. Typical load    | performance. Typical load    | to test.                  |

|                 | scenarios are not            | scenarios are not sufficient |                           |

|                 | sufficient to test properly. | to test properly.            |                           |

| Extensibility   | The need to recalculate      | The response time analysis   | Neither method makes it   |

|                 | static schedules is          | will need to be recomputed   | easier to extend the      |

|                 | necessary if adding          | if added functionality is    | functionality of the      |

|                 | functions.                   | introduced to the system.    | system.                   |

| Fault-Tolerance | Different nodes can make     | It is harder to achieve a    | In general time-triggered |

|                 | the same decision at the     | fault-tolerant system unless | systems provide more      |

|                 | same time.                   | a leader-follower system is  | fault-tolerance within a  |

|                 |                              | used.                        | system.                   |

| Resource        | A node is seen as            | A resource will only be      | Event-triggered systems   |

| Utilisation     | redundant during any         | requested when needed.       | can maximise the          |

|                 | communication cycle if it    |                              | resource in more cases    |

|                 | has nothing to send. This    |                              | than time-triggered       |

|                 | means there is wasted        |                              | systems                   |

|                 | resources.                   |                              |                           |

Table 3.2: Event-triggered vs. time-triggered systems

#### **3.4 Automotive Network Protocols**

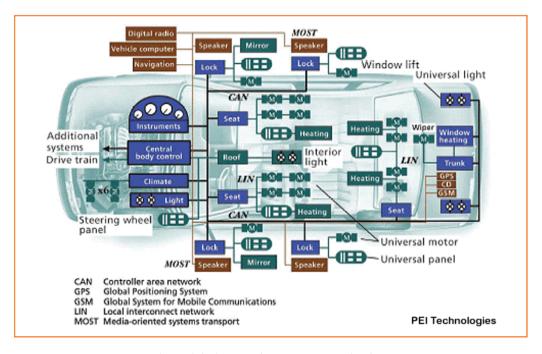

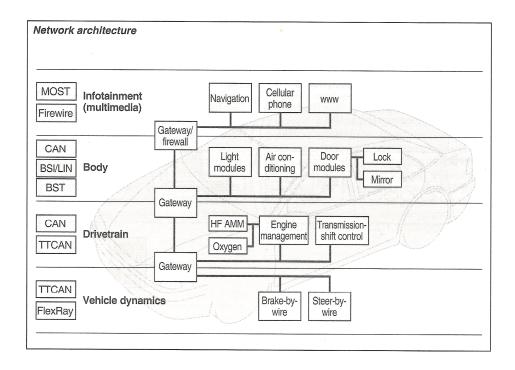

Figure 3.3 (Leen and Heffernan 2002, p89) shows a breakdown of the types of systems implemented electronically in cars. Figure 3.4 (Denner et. al. 2004) shows the functional area breakdown for each networking scheme.

Figure 3.3: Automotive network applications

Figure 3.4: Automotive networks functionality breakdown

As can be seen from Figures 3.3 and 3.4, there is no one networking scheme that is designed to carry out all necessary communications. It is can also be seen that with

the present situation, automotive electronic and electrical systems need a proper communications network to communicate. Without any multiplexed communications systems there would be a huge amount of wiring dedicated to the transmission of information between two specific nodes. The inclusion of an interconnected multiplexed communication network also reduces the number of duplicate sensors in a vehicle. In a multiplexed networking scheme sensor data can be shared to a number of different nodes all at the same time. The reduction in the number of duplicate sensors has a cost saving benefit for the manufacturer and customer. Without a multiplexed networking system a vehicle would be seen as having a drastic weight increase and thus relatively poor performance of the vehicle, in terms of both power and fuel economy, when compared to a vehicle where a multiplexed networking system is implemented.

#### 3.5 Event-Triggered Protocols

#### 3.5.1 Controller Area Network (CAN)

The CAN networking scheme was first introduced in 1986. It was developed by Bosch with help from Mercedes-Benz and Intel. The development of the protocol was started as early as 1983 in a bid to increase functionality for the automotive industry. The reduction in wiring within a vehicle was a consequence of the protocol. Since it was introduced it has been used in a wide range of applications within cars as well as in other areas. Most cars produced in Europe will contain at least one CAN. It has been used in trains, ships and industrial control applications (CiA 2007). It has even been implemented in the 2008 BMW RG 1200 GS Adventure motorcycle (BMW Motorrad USA 2008).

In 1991 the CAN specification 2.0 was published by Bosch. In 1993 CAN was standardised as ISO 11898 by the International Organisation of Standards with an extended frame format being standardised with an amendment in 1995. A time triggered communication protocol for CAN (TTCAN) was developed in 2000 (CiA 2007).

#### 3.5.1.1 CAN Protocol

This section is a combination of information from Denner et. al. (2004), Carley (2006), CiA (2006), Schofield (2006), Robert Bosch GmbH (1991) and Jurgen (1999).

The CAN bus is made up of a number of ECUs that all have a priority rating. A CAN bus can be seen in Figure 3.5 (Ecartec Ltd. 2008). Figure 3.5 depicts different nodes connected onto the same CAN bus. Each node performs a different function.

Figure 3.5: CAN Bus

To determine which node may communicate at any one time an identifier field is used in the message frame. The node with the highest priority will be allowed to transmit its message. When several nodes attempt to transmit a message at the same time the message with the highest priority will gain access without any delay. This is due to the 'wired-AND' bus arbitration. As the arbitration is based on a logical 'AND' operation, the lowest the message identifier has the highest message priority. In this way dynamic transmission is achieved. The diagram below, Figure 3.6 (Softing 2008), shows how a logic '0' ensures that a low message identifier ensures a higher priority.

Node 3 wins arbitration and transmits his data.

Figure 3.6: CAN bus arbitration

After a message is transmitted the nodes can again attempt to gain access to the bus.

The CAN protocol supports two frame formats, standard and extended. The message format is similar for both protocols, differing only in the number of identifier bits. Figure 3.7 (Schofield 2006), shows the standard frame format, which contains 11 identifier bits. For the extended frame format the main difference is that the identifier contains 29 bits. This means that the frames vary in length between 130 to 150 bits (maximum). The data segment however is limited to 0 to 64 bits (8 bytes).

Figure 3.7: CAN standard frame format

The segments of a CAN message are as follows:

- SOF: Start of Frame bit.

- Arbitration field that consists of the identifier and a remote frame indicator.

- The control field indicates the number of data bytes in the message.

- The data field contains 0 8 bytes of data.

- The CRC field is a 15 bit cyclic redundancy check (CRC) used by the receiving node to detect any errors in the received frame.

- The ACK field is to allow all receivers to acknowledge error free reception of the message.

- The end of frame bits indicate the end of transmission of the frame.

- Int is the inter frame space where data is not to be transmitted to ensure frame integrity.

## 3.5.2 Local Interconnect Network (LIN)

The local interconnect network (LIN) is a deterministic system for ECU communication with sensors, actuators and controls. The LIN specification version 2.1 was released in 2006. In August of 2004 the Society of Automotive Engineers (SAE) released J2606 which recommends a practice for implementing LIN (Vector Informatik GmbH 2008, p1).

A LIN network always consists of one master node and a number of slave nodes. It is designed so it can easily be interfaced, through a gateway, to other communication busses such as CAN (Ahlmark 2000, p1). Figure 3.8 (Ahlmark 2000, p4) shows a LIN bus configuration.

Figure 3.8: LIN bus with single master node and 'n' slave nodes

The LIN protocol operates as a Master/Slave configuration. Only the master is able to initiate communication. A LIN frame consists of a header and response sections. Communication with a slave involves the master sending the header part of a message. If the master wants to send data to the slave it continues to send the response part. If the

master requests data from the slave the slave sends the response part (STMicroelectronics 2001, p4).

The header section of the frame consists of a break field, sync field and a frame identifier. The frame identifier uniquely defines the frame. The break field is used to identify the start of a transmission and the sync field is to allow receiving nodes to synchronise with the transmitted bits (LIN Consortium 2006, p29). The slave task, configured to provide the response associated with the frame identifier, will begin transmission as depicted in Figure 3.9 (LIN Consortium 2006, p13). The response consists of a data field and a checksum field. All slave nodes interested in the data associated with the frame identifier receives the response, verifies the checksum and uses the data received (LIN Consortium 2006, p13). This broadcast scheme operates at speeds up to 20kbits/s (Ahlmark 2000, p4).

Figure 3.9: LIN communication

## 3.5.3 Media Oriented Systems Transport (MOST)

Media Orientated Systems Transport (MOST) is a protocol that has been developed to handle high volume data transfer. This is usually in the form of 'infotainment' data for audio and visual devices. Currently MOST is implemented using a plastic optical fiber (POF) communication bus. This provides a number of advantages such as weight saving and protection from electromagnetic interference. However there is also an electrical physical specification (TechInsights 2008).

MOST does not require a reconfiguration of the topology if new systems are added. The extra components can simply be added into the network by adding a connector to the physical bus. In this way MOST can be seen to have a plug and play approach to system integration (TechInsights 2008).

MOST can operate at two different speeds. There are 25Mbit/s and 50Mbit/s speed grades specified (MOST Cooperation 2006, p16). There are also a number of

different communication channels over which data can be transmitted. These are as follows (MOST Cooperation 2006, pp17-18):

- Control Channel: This channel is used for small data frames with 'bursty' like transmission. The data rate for this channel is a relatively low 10kbits/s. The data is transported to a specific address and is protected by a CRC just like the packet data channel.

- Streaming Data Channel: This is used for continuous data such as data from an audio or video device.

- Packet Data Channel: This channel is defined for large 'bursty' traffic. This

could be in the form of navigational map images.

- Management Streaming/Package Bandwidth: In a MOST system the management streaming and packet data streaming can be allocated space on the overall bandwidth.

A MOST system can have up to 64 nodes. Any of these nodes can be the TimingMaster and all the other nodes are Slaves. The TimingMaster provides generation and transportation of the system clock, the frames, and blocks. All Slave devices derive their clock from the MOST bus (MOST Cooperation 2006, p106). In this way MOST is a Master/Slave protocol.

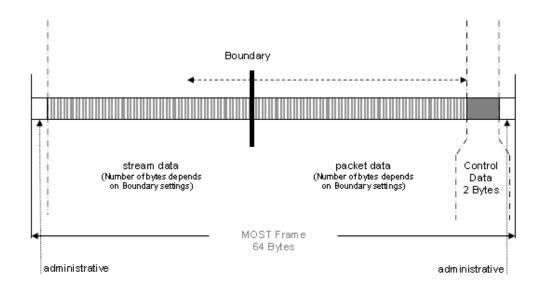

One MOST25 (the 25Mbit/s variant) frame consists of 64 bytes. The first byte is used for administrative purposes. The next 60 bytes are used for Stream and Packet Data Transfer. A Boundary section of the header defines in 4 byte steps the number of data bytes. The Boundary value can only have values between 6 and 15. This means at least 24 bytes are available for Stream data transfer. All Stream data bytes are transmitted before the Packet data bytes. The next two bytes of each frame are reserved for Control data and the last byte is another administrative byte (MOST Cooperation 2006, p108). Figure 3.10 (MOST Cooperation 2006, p108) and Table 3.3 (MOST Cooperation 2006, p108) show and describe the MOST25 data frame.

Figure 3.10: MOST25 frame

| Byte Number | Task                                    |  |  |

|-------------|-----------------------------------------|--|--|

| 0           | Administrative                          |  |  |

|             | * Preamble (bits 0-3)                   |  |  |

|             | * 4 bits Boundary Descriptor (bits 4-7) |  |  |

| 1 - 60      | 60 data bytes                           |  |  |

| 61 - 62     | 2 data bytes for Control Messages       |  |  |

| 63          | Administrative                          |  |  |

|             | * Frame control and status bits         |  |  |

|             | * Parity bit (last bit)                 |  |  |

Table 3.3: MOST25 frame byte summary

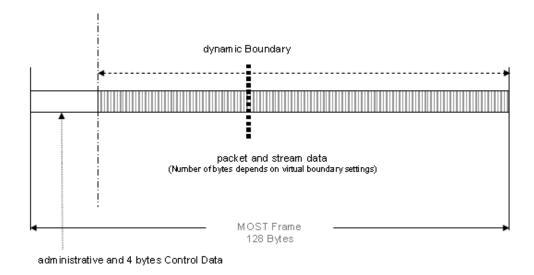

MOST50 is designed for high bandwidth, and one MOST50 frame consists of 128 bytes. The first 11 bytes are used for administrative purposes. Within this 4 bytes are used for Control data. The Control Message length can vary depending on the actual control message to be sent. Better utilisation of the bandwidth regarding Control Messages is obtained in this way. The next 117 bytes are used for Packet and Stream data transfer (MOST Cooperation 2006, p108). Figure 3.11 (MOST Cooperation 2006, p109) and Table 3.4 (MOST Cooperation 2006, p109) show and describe the MOST50 data frame.

Figure 3.11: MOST25 frame

| Byte Number | Task                                                        |

|-------------|-------------------------------------------------------------|

| 0 - 10      | Administrative, includes 4 Control data bytes, additionally |

|             | * System Lock flag                                          |

|             | * Boundary Descriptor                                       |

| 11 - 127    | 117 data bytes                                              |

Table 3.4: MOST25 frame byte summary

# 3.6 Time-Triggered Protocols

Car manufactures faced a problem when attempting to implement new safety-critical applications in cars using event-triggered communication systems. For instance, in a brake-by-wire system it is important to determine the greatest latency experienced in the system. It is important to know that when a driver presses the brake pedal the system will respond within a given time. The most widely used communication protocol in the automotive industry (CAN) is an event-driven communication protocol. This leads to an inability to determine the worst case scenario. Higher priority messages could potentially always block a message. This led to the need for a new protocol specification. By dividing up the available bandwidth into time slots a more deterministic protocol could be achieved. Two time-triggered protocols will be discussed in this section, namely TTP and FlexRay.

## 3.6.1 Time-Triggered Protocol (TTP)

This section is based on the works of Böhm (2005), Elmenreich and Ipp (2003) and Elemenrich and Krywult (2005).

TTP/A and TTP/C are two real-time protocols based on a TDMA scheme. TDMA (Time Division Multiple Access) is a method of multiplexing a single communication medium. To allow multiple nodes in a network to gain access to the communications bus each node is allocated a time slice. During this time slice or slot the node may transmit its message. If a node wants to transmit a message it must wait for the assigned slot to come around. When a node is not transmitting a message it can receive messages from other nodes. TTP/C is intended for connecting a number of nodes to achieve a dependable real-time system. TTP/A is a lower cost version and has reduced functionality. It is intended to use TTP/A as a bus to connect sensors and actuators.

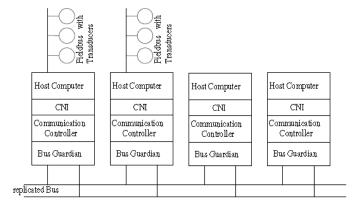

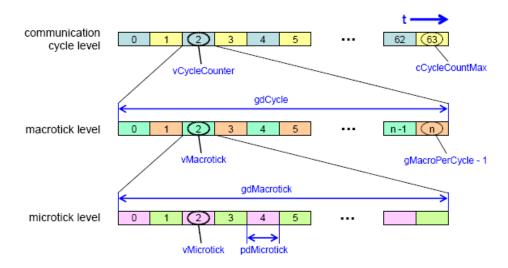

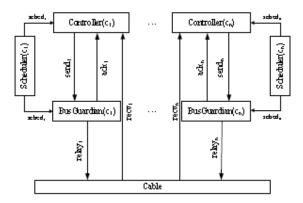

In TTP/C the frame size can vary between 2 and 240 bytes. Each frame can carry a number of messages. In different communication rounds different messages can be transmitted during a node's allocated slot. The data is protected by a 24 bit CRC. To ensure each node sends its frame during the correct time slot the use of a bus guardian is employed. This is a separate component to the communication controller. The bus topology can be seen in Figure 3.12 (Elemenreich and Ipp 2003,P2). A star topology can also be employed. The star topology implements two stars that also act as central guardians for the network. In Figure 3.12, the CNI layer is a connection between the communications controller and the host computer. This encompasses all necessary physical connections as well as any software driver used.

Figure 3.12: TTP bus topology

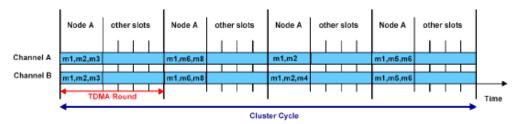

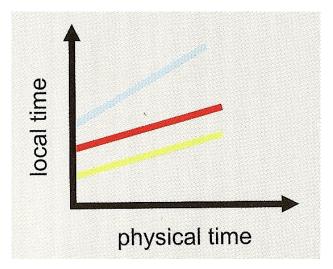

To ensure that each node transmits at the allocated time the bus guardian must have a global view of the time. The current view of the global time is obtained using a clock synchronisation algorithm. This algorithm determines the current time based on the arrival of frames from other nodes and the expected time of arrival of the frames. Figure 3.13 below shows the TTP communication cycle (Elemenreich and Ipp 2003, P4).

Figure 3.13: TTP communication cycle

From the TTA Group website (TTA-Group 2008), it can be seen that TTP is still found in various applications. The main area that TTP is used for appears to be in aerospace applications.

# 3.6.2 FlexRay

The FlexRay protocol was developed after BMW and DaimlerChrysler worked together to develop a networking scheme for future developments such as drive-by wire applications. The partnership soon led to a protocol specification which is the basis for FlexRay systems (FlexRay Consortium 2007). Due to the fact that BMW was heavily involved in the development and its similar characteristics, FlexRay can be seen as a legacy protocol of 'byteflight'. Byteflight was also developed by BMW and uses both time-triggered and event-triggered access to the communication bus (BMW 2000).

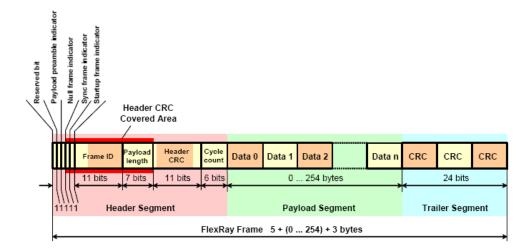

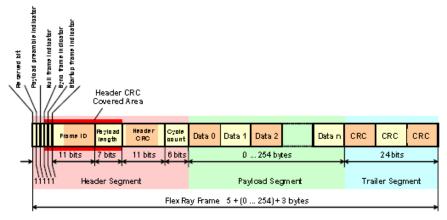

Like TTP, FlexRay is based on a TDMA approach. If a node wishes to transmit a message it must wait until its communication slot comes around. It may then transmit a single message that can consist of a data section of between 0 and 254 bytes. The header of a message is protected by an 11 bit CRC while the frame as a whole is protected by a 24 bit CRC. The frame format can be seen in Figure 3.14 (FlexRay Consortium 2005, p.90). The communication cycle is divided into 4 segments. These

segments allow the nodes to transmit in a time-triggered way as well as an event-triggered fashion.

Figure 3.14: FlexRay frame

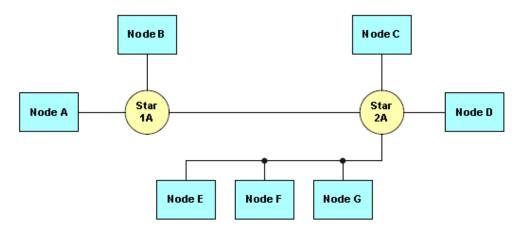

A FlexRay network supports bus and star topologies just as TTP does. However it also supports hybrid topologies. This can be seen in Figure 3.15 (FlexRay Consortium 2005, p.24).