## **Waterford Institute of Technology**

# PERFORMANCE ANALYSIS OF AUTOSAR VEHICLE NETWORK GATEWAYS

B.Sc. (Hons)

M.Sc.

Supervisor: Brendan Jackman B.Sc., M.Tech.

Submitted to Waterford Institute of Technology Awards Council, July 2007

#### **ACKNOWLEDGEMENTS**

This thesis would have been impossible without the help of the following people.

Firstly, I would like to thank Mr. Brendan Jackman for his encouragement and guidance throughout this project.

I would like to thank Dr. Darren Buttle, ETAS LiveDevices, for his guidance throughout this project.

I would also like to thank the members in our group for their valuable advices and help.

- David Power, Group Supervisor, Department of Computing, Maths & Physics, Waterford Institute of Technology

- Frank Walsh, Group Supervisor, Department of Computing, Maths & Physics, Waterford Institute of Technology

- Kevin Mullery, Group Member, Department of Computing, Maths & Physics,

Waterford Institute of Technology.

Finally, I will like to thank my wonderful Parents, and all my friends for encouragement throughout this time.

### **DECLARATION**

Zhu WeiDa

I, 朱 章達, declare that this thesis is submitted by me in partial fulfillment of the requirement for the degree M.Sc., is entirely my own work except where otherwise accredited. It has not at any time either whole or in part been submitted for any other educational award.

| Signature: |  |  |  |

|------------|--|--|--|

|            |  |  |  |

Zhu WeiDa

朱 韋達,

May 27th, 2007.

#### **ABSTRACT**

Modern vehicles use a variety of data networks to exchange data between their different control modules. These networks operate at different communication speeds to reflect the relative response times of the connected control units. For example, engine control units are connected to a high-speed network while comfort systems such as electric seats are connected to a low speed network. In addition, there are a number of different network operating principles, for example, event-driven and time-triggered. Gateways are required to exchange data between these different vehicle networks. Gateways typically exchange messages between connected networks based solely on the destination and priority of the messages. Such gateways can result in unpredictable message delays depending on the network loading and vehicle operating conditions.

The aim of this research is to develop and evaluate a vehicle network gateway model based on a very general and well designed gateway structure from the automotive industry, which takes into account factors such as the purpose of network messages, vehicle operating conditions, network loading, bus topology and message streams.

The network gateway model is used to evaluate the relative performance of different gateway configurations.

## TABLE OF CONTENTS

| ACKNO         | VLEDGEMENTS                                   | I    |

|---------------|-----------------------------------------------|------|

|               | PATION                                        |      |

| ABSTRA        | CT                                            | III  |

| TABLE (       | OF CONTENTS                                   | IV   |

| TABLE (       | OF FIGURES                                    | VIII |

| TABLE (       | OF TABLES                                     | X    |

|               | SIS OVERVIEW                                  |      |

| 1.1           | PROBLEM SPECIFICATION                         |      |

| 1.2           | SOLUTION REQUIREMENTS                         |      |

| 1.3           | RESEARCH QUESTIONS                            |      |

| 1.4           | DOCUMENT LAYOUT                               | 4    |

| 2. <b>VEH</b> | ICLE NETWORK PROTOCOLS                        | 6    |

| 2.1 IN        | TRODUCTION                                    | 6    |

| 2.2 Ev        | VENT AND TIME TRIGGERED COMMUNICATION SYSTEMS | 8    |

|               | ONTROLLER AREA NETWORK – CAN                  |      |

| 2.3.1         | CAN AND THE OSI MODEL                         | 9    |

| 2.3.2         | BUS ARBITRATION                               | 10   |

| 2.3.3         | CAN Bus Architecture                          | 11   |

| 2.3.4         | MESSAGE AND FRAME FORMATS                     | 12   |

| 2.3.4.        | 1 Data Frame                                  | 12   |

| 2.3.4.        | 2 REMOTE FRAME                                | 14   |

| 2.3.4.        | 3 Error Frame                                 | 14   |

| 2.3.4.        | 4 Overload Frame                              | 15   |

| 2.3.4.        | 5 ERROR DETECTION                             | 15   |

| 2.3.5         | TIME-TRIGGERED CAN (TTCAN)                    | 18   |

| 2.4 Lo        | OCAL INTERCONNECT NETWORK – LIN               | 20   |

| 2.4.1         | LIN BUS TECHNICAL OVERVIEW                    | 20   |

| 2.4.2         | LIN PROTOCOL CONCEPT                          | 20   |

| 2.4.3         | LIN SPECIFICATION                             | 22   |

| 2.5 FI        | EXRAY                                         | 24   |

| 2.5.1         | FLEXRAY ADVANTAGES                            | 24   |

| 2.5.2         | FLEXRAY APPLICATIONS                          | 27   |

| 2.5.3         | FLEXRAY PROTOCOL                              | 27   |

| 2.5.3.        | 1 FLEXRAY NODE OPERATION                      | 28   |

| 2.53          | 2 FRAME FORMAT AND SIGNALS                    | 30   |

|    | 2.6 RE | FERENCES                                               | 32 |

|----|--------|--------------------------------------------------------|----|

| 3. | VEHI   | CLE NETWORK DESIGN                                     | 33 |

|    | 3.1    | Introduction                                           | 33 |

|    | 3.2    | NETWORK TOPOLOGIES                                     | 34 |

|    | 3.3    | NETWORK GATEWAYS                                       | 37 |

|    | 3.4    | NETWORK DESIGN METHODOLOGIES                           | 39 |

|    | 3.4.1  | BASIC NETWORK DESIGN METHODOLOGIES                     | 39 |

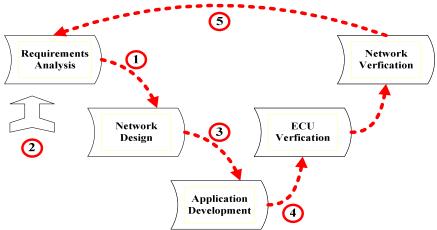

|    | 3.4.2  | In-vehicle Network Design Methodologies                | 40 |

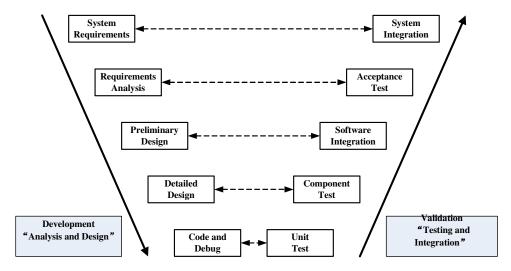

|    | 3.4.3  | V MODEL                                                | 45 |

|    | 3.4.4  | TRADITIONAL DESIGN PROCESS AND ADVANCED DESIGN PROCESS | 46 |

|    | 3.5    | NETWORK MANAGEMENT                                     | 52 |

|    | 3.5.1  | OSEK/VDX                                               | 52 |

|    | 3.5.2  | OSEK/VDX NETWORK MANAGEMENT                            | 53 |

|    | 3.5.3  | OSEK/VDX NETWORK MANAGEMENT COMPONENTS                 | 53 |

|    | 3.6    | Conclusion                                             | 55 |

|    | 3.7    | References                                             | 56 |

| 4. | NETV   | VORK GATEWAY DESIGN                                    | 57 |

|    | 4.1    | Introduction                                           | 57 |

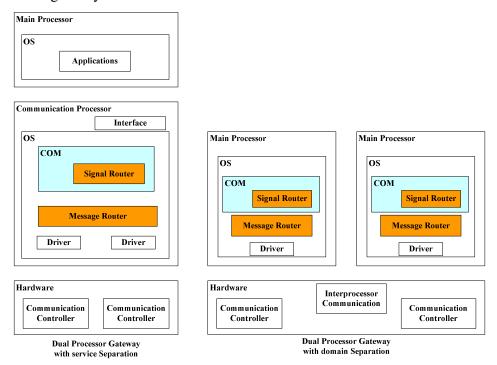

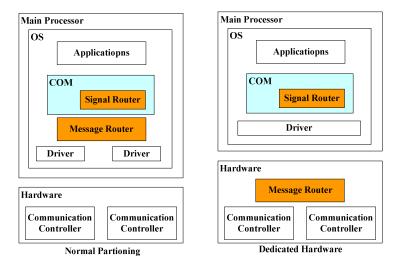

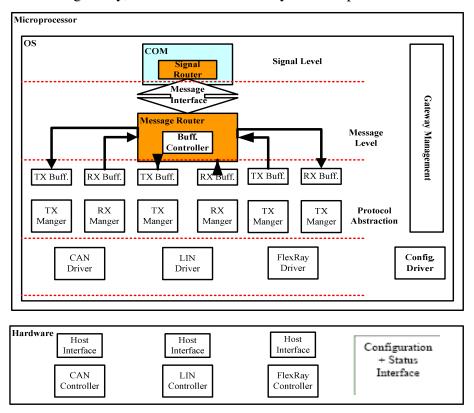

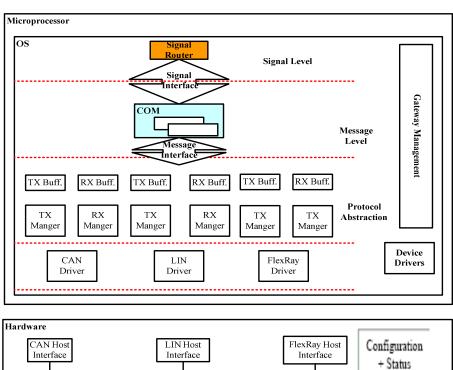

|    | 4,2    | GATEWAY HARDWARE ARCHITECTURES                         |    |

|    | 4.2.1  | GENERAL GATEWAYS ANALYSIS                              |    |

|    | 4.2.2  | GATEWAY ARCHITECTURES                                  |    |

|    | 4.3    | GATEWAY SOFTWARE MODULES                               | 63 |

|    | 4.4    | OPTIMIZATION OF GATEWAY PERFORMANCE                    | 65 |

|    | 4.4.1  | USING OF ROUTERS FOR OPTIMIZING GATEWAY PERFORMANCE    |    |

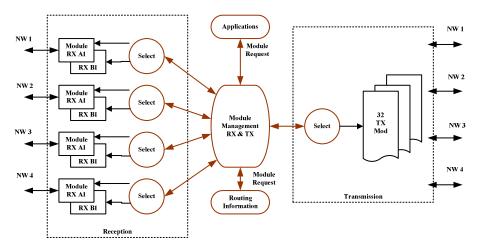

|    | 4.4.2  | HARDWARE/SOFTWARE PARTITIONING AND ROUTING LEVELS      | 65 |

|    | 4.4.3  | ROUTER STRUCTURE IN GATEWAYS                           |    |

|    | 4.4.4  | DEDICATED HARDWARE FOR ROUTER                          |    |

|    | 4.4.5  | PROTOCOL ANALYSIS                                      | 72 |

|    | 4.5    | Conclusion                                             | 74 |

|    | 4.6    | References                                             | 75 |

| 5. | SIMU   | LATION                                                 | 76 |

|    | 5.1    | Introduction                                           | 76 |

|    | 5.2    | SIMULATION METHODOLOGIES                               |    |

|    | 5.3    | SIMULATION TECHNOLOGY                                  |    |

|    | 5.3.1  | THE BASIC QUEUING THEORY                               |    |

|    | 5.3.2  | MARKOV PROCESS AND ITS MAJOR MODELS                    |    |

|    | 5321   |                                                        | 82 |

|    | 5.3.2.2 | DISCRETE AND CONTINUOUS MARKOV PROCESS                 | 84  |

|----|---------|--------------------------------------------------------|-----|

|    | 5.3.2.3 | Examples of Queuing Models                             | 84  |

|    | 5.4     | SIMULATION TOOL – MATLAB/SIMULINK AND SIMEVENTS        | 87  |

|    | 5.4.1   | BACKGROUND                                             |     |

|    | 5.4.2   | THE MATLAB SYSTEM                                      |     |

|    | 5.4.3   | SIMULINK AND STATEFLOW                                 | 90  |

|    | 5.4.4   | SIMEVENTS                                              | 90  |

|    | 5.4.4.1 | SIMEVENTS QUEUES AND SERVERS                           | 91  |

|    | 5.4.4.2 | SIMEVENTS PATHS AND ROUTING TECHNIQUES                 | 92  |

|    | 5.6     | CONCLUSION                                             | 93  |

|    | 5.7     | REFERENCES                                             | 94  |

| 6. | LITER   | ATURE REVIEW SUMMARY                                   | 95  |

| 7. | METH    | IODOLOGY                                               | 96  |

|    | 7.1     | METHODOLOGY OVERVIEW                                   | 96  |

|    | 7.2     | SIMULATION DESIGN                                      | 97  |

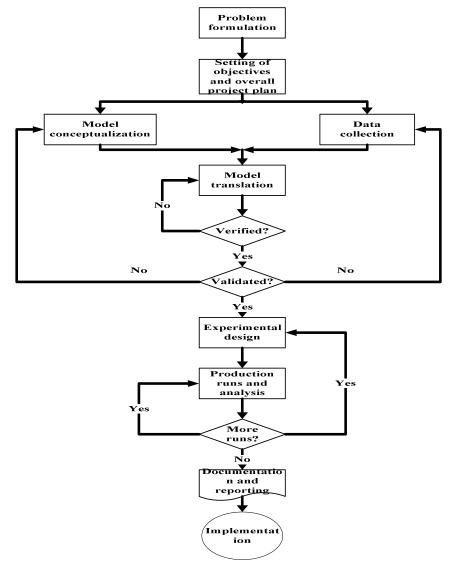

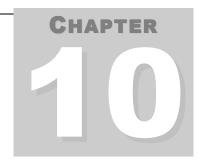

|    | 7.2.1   | SIMULATION PROCESS                                     | 97  |

|    | 7.2.2   | SIMULATION PROCESS RELATED TO THIS RESEARCH            | 100 |

|    | 7.3     | SIMULATION TOOL SELECTION                              | 103 |

|    | 7.4     | CONCLUSION                                             | 105 |

|    | 7.5     | REFERENCES                                             | 106 |

| 8. | GATE    | WAY MODEL REQUIREMENTS SPECIFICATION                   | 107 |

|    | 8.1     | SYSTEM ARCHITECTURE OVERVIEW                           | 107 |

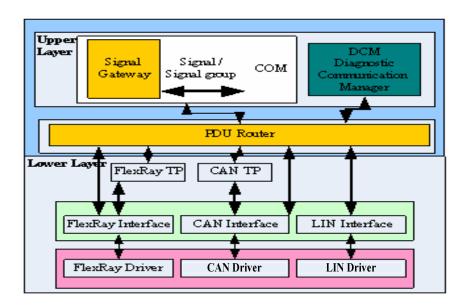

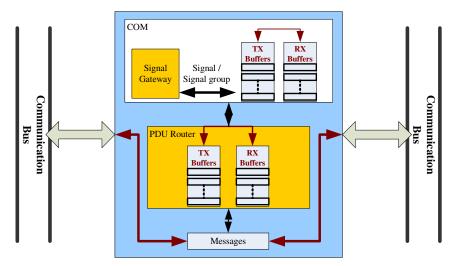

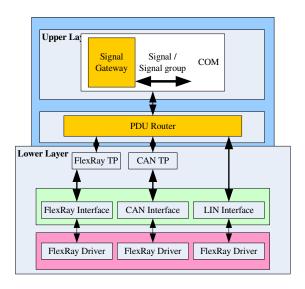

|    | 8.2     | AUTOSAR GATEWAY STRUCTURE                              | 108 |

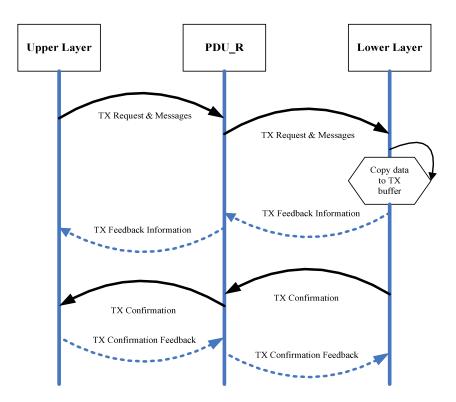

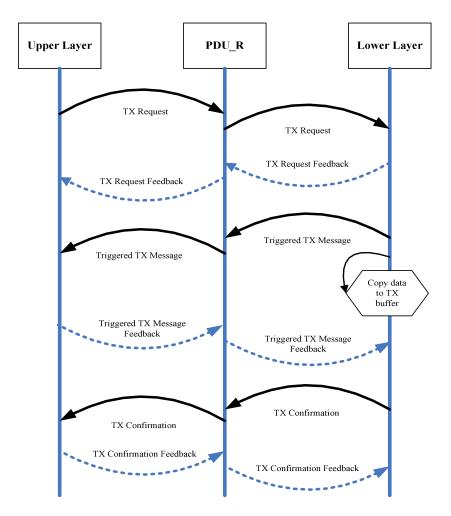

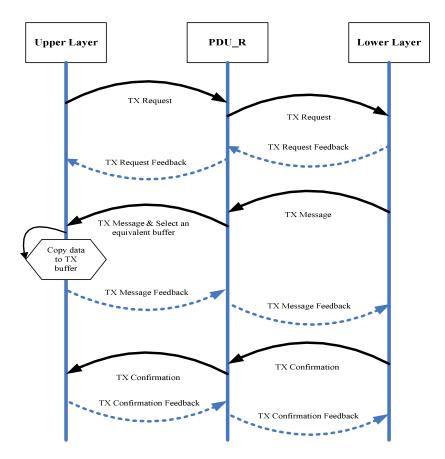

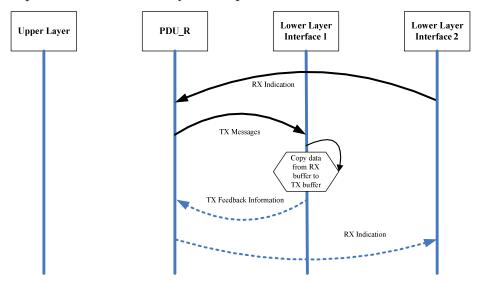

|    | 8.2.1   | MESSAGE TRANSMISSION TYPES                             | 110 |

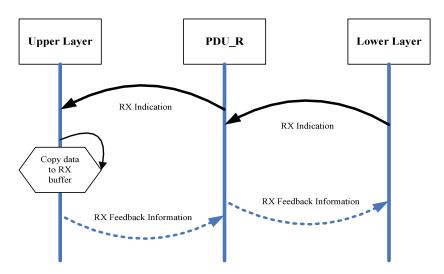

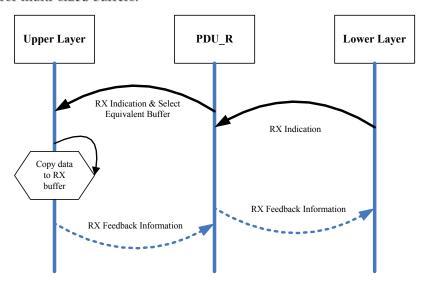

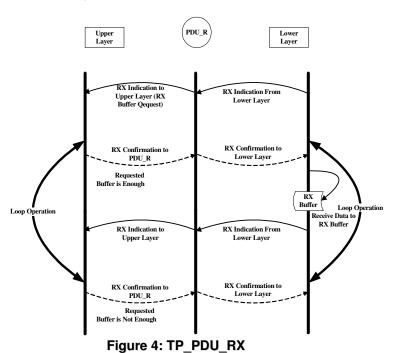

|    | 8.2.2   | MESSAGE RECEPTION TYPES                                | 113 |

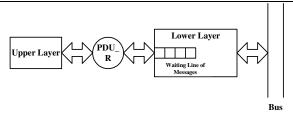

|    | 8.2.3   | AUTOSAR PDU ROUTER                                     |     |

|    | 8.3     | GATEWAY BUFFER REQUIREMENTS                            | 118 |

|    | 8.4     | CONCLUSION                                             | 119 |

|    | 8.5     | REFERENCES                                             | 120 |

| 9. | SIMU    | LATION MODEL DESIGN AND IMPLEMENTATION                 | 121 |

|    | 9.1     | Introduction                                           | 121 |

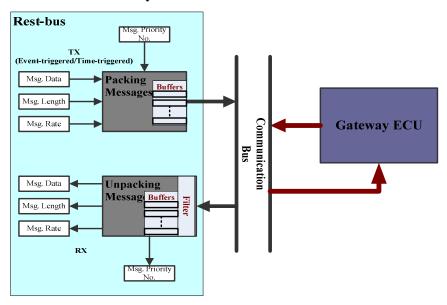

|    | 9.2     | REST BUS SIMULATION MODEL                              | 123 |

|    | 9.2.1   | COMMUNICATION BUS SIMULATION MODEL                     | 124 |

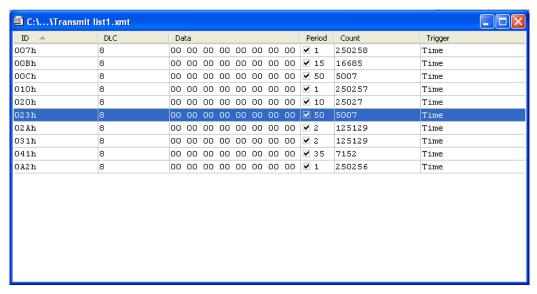

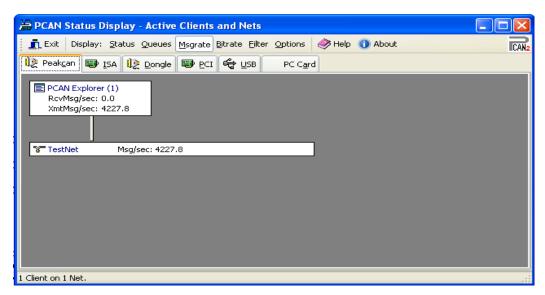

|    | 9.2.2   | EXPERIMENTAL MEASUREMENT OF MESSAGE TRANSMISSION TIMES | 124 |

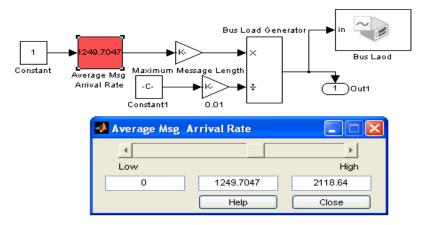

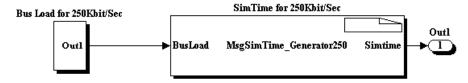

|    | 9.2.3   | BUS LOAD SIMULATION                                    | 128 |

|    | 024     | Messace Transmission Time Similiation                  | 130 |

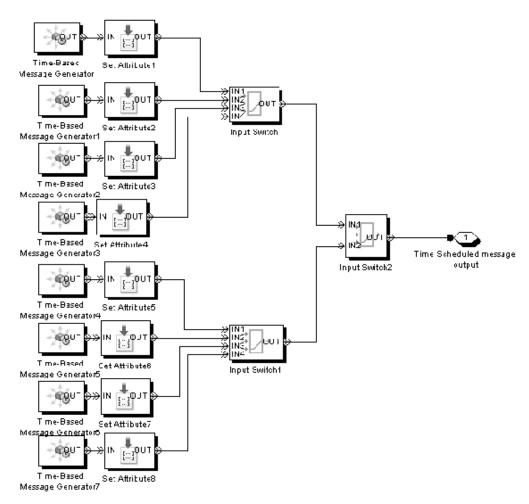

|    | 9.2.5          | TIME-TRIGGERED BUS SIMULATION MODEL                                             | 131 |

|----|----------------|---------------------------------------------------------------------------------|-----|

|    | 9.3            | AUTOSAR GATEWAY SIMULATION MODEL                                                |     |

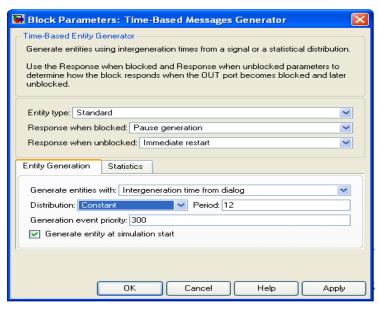

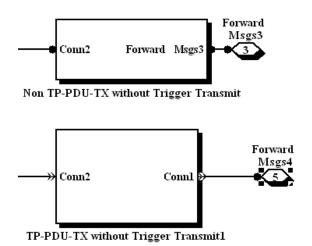

|    | 9.3.1          | COM MESSAGE GENERATION                                                          |     |

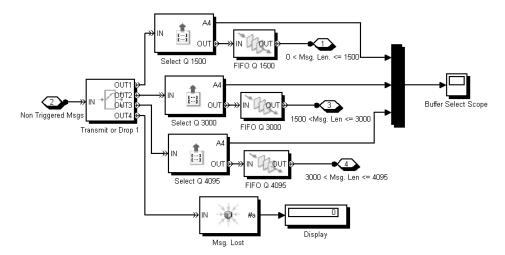

|    | 9.3.2          | BUFFER SELECTION                                                                |     |

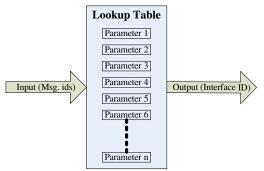

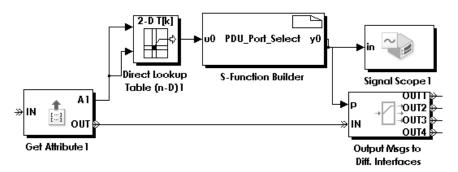

|    | 9.3.3          | MESSAGE ROUTING                                                                 |     |

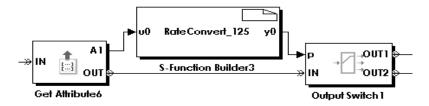

|    | 9.3.4          | RATE CONVERSION                                                                 |     |

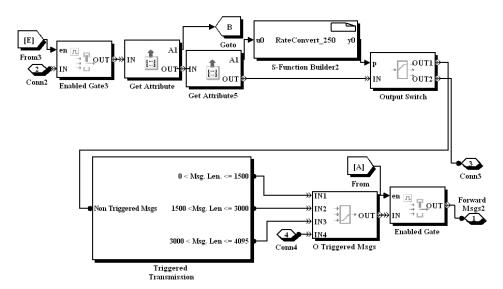

|    | 9.4            | TRANSMISSION TYPE MODELLING                                                     |     |

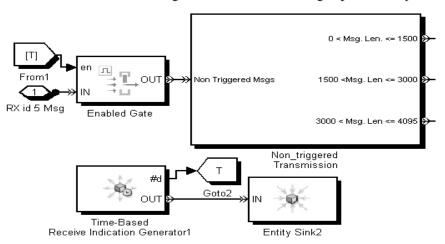

|    | 9.5            | RECEPTION TYPE MODELLING                                                        |     |

|    | 9.6            | SIMULATION MODEL DESIGN VALIDATION COMMENTS – FROM AN EXPERT IN MOTIVE INDUSTRY |     |

|    | 9.7            | References                                                                      |     |

| 10 | ). <b>T</b> E: | STING                                                                           | 146 |

|    | 10.1           | Introduction                                                                    |     |

|    | 10.2           | TESTING TOOLS                                                                   |     |

|    | 10.2.          |                                                                                 |     |

|    | 10.2.2         |                                                                                 |     |

|    | 10.3           | VERIFICATION OF GATEWAY SIMULATION MODEL                                        | 150 |

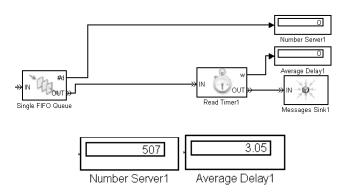

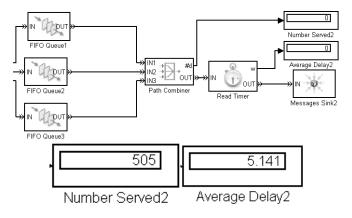

|    | 10.4           | VERIFICATION TESTING CASES                                                      | 151 |

|    | 10.5           | VALIDATION OF GATEWAY SIMULATION MODEL                                          | 159 |

|    | 10.5.          | OBJECT OF VALIDATION                                                            | 159 |

|    | 10.5.2         | 2 VALIDATION PROCEDURE                                                          | 159 |

|    | 10.6           | OPTIMISATION OF GATEWAY PERFORMANCE                                             | 164 |

|    | 10.6.          | EVALUATION CASES TABLE                                                          | 164 |

|    | 10.6.2         | 2 EVALUATION CASES                                                              | 164 |

|    | 10.7           | Conclusion                                                                      | 181 |

|    | 10.8           | REFERENCES                                                                      | 182 |

| 11 | 1. <b>Co</b>   | NCLUSIONS                                                                       | 183 |

|    | 11.1           | RESEARCH SUMMARY                                                                | 183 |

|    | 11.2           | RESEARCH CONCLUSION                                                             | 185 |

|    | 11.3           | AREAS FOR FURTHER RESEARCH                                                      | 187 |

| 12 | 2. <b>AP</b>   | PENDIX A BIBLIOGRAPHY                                                           | 188 |

|    | 12             | Bibliography                                                                    | 188 |

| 13 |                | PENDIX B SAE PAPER                                                              | 192 |

|    |                | SAE PAPER                                                                       | 192 |

|    |                |                                                                                 | _   |

# TABLE OF FIGURES

| Figure 2.1: OSI model and layered architecture of CAN                     | 9  |

|---------------------------------------------------------------------------|----|

| Figure 2.2: CAN bus Arbitration                                           | 11 |

| Figure 2.3: CAN network according to ISO 11898                            | 11 |

| Figure 2.4: Data Frame                                                    | 12 |

| Figure 2.5: Remote Frame                                                  | 14 |

| Figure 2.6: Error State Diagram of a CAN node                             | 17 |

| Figure 2.7: TTCAN Message Schedule                                        | 19 |

| Figure 2.8: LIN bus topology                                              | 20 |

| Figure 2.9: LIN bus transmission cycle                                    | 21 |

| Figure 2.10: LIN Frame                                                    | 21 |

| Figure 2.11: LIN Bus Tool Chain                                           | 23 |

| Figure 2.12: FlexRay Topologies                                           | 24 |

| Figure 2.13: Comparisons of Protocol Data Rates                           | 26 |

| Figure 2.14: FlexRay Node                                                 | 28 |

| Figure 2.15: FlexRay State Transitions                                    | 29 |

| Figure 2.16: FlexRay Error State Transitions                              | 30 |

| Figure 2.17: FlexRay frame format                                         | 30 |

| Figure 3.1: Star Topology                                                 | 35 |

| Figure 3.2: Bus Topology                                                  | 35 |

| Figure 3.3: Ring Topology                                                 | 36 |

| Figure 3.4: Central Gateway                                               | 38 |

| Figure 3.5: Multi Gateways                                                | 38 |

| Figure 3.6: Backbone Gateways                                             | 38 |

| Figure 3.7: Design Flow Process                                           | 39 |

| Figure 3.8: Network Design Process                                        | 41 |

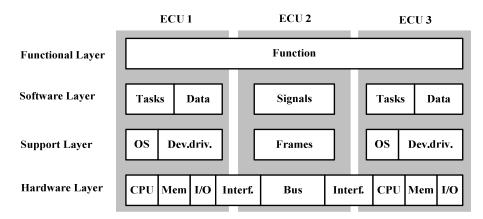

| Figure 3.9: Example of Functional Allocation                              | 43 |

| Figure 3.11: the V Model                                                  | 46 |

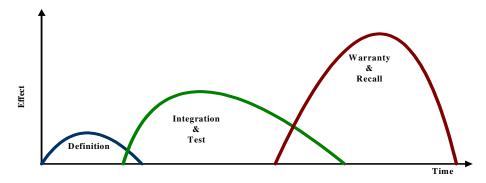

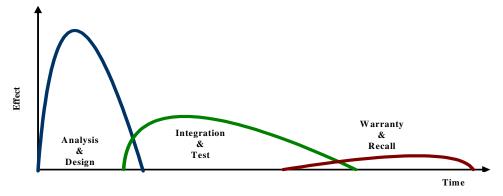

| Figure 3.12: Traditional Network Design Process Effect                    | 49 |

| Figure 3.14: Traditional V Model                                          | 50 |

| Figure 3.15: Advanced V Model                                             | 51 |

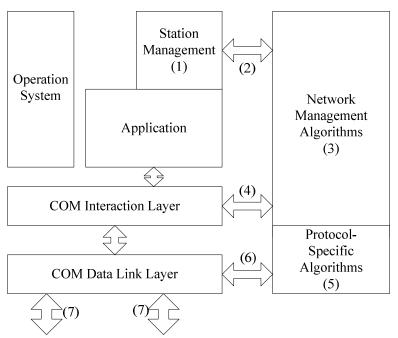

| Figure 3.16: In-vehicle Network Management Environment                    |    |

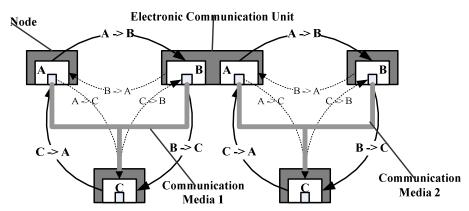

| Figure 3.17: NM equipment with two CAN systems                            |    |

| Figure 4.1: The Basic Structure of Fail Silent Units (FSU)                | 59 |

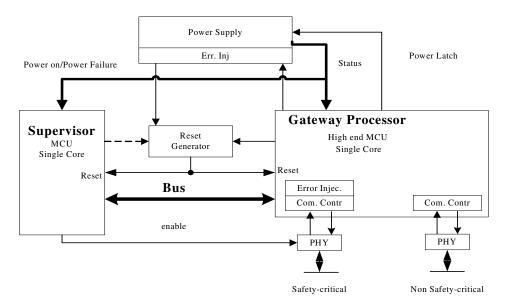

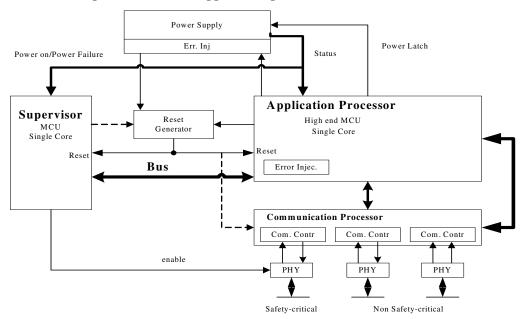

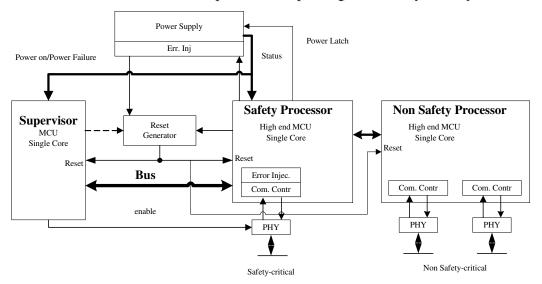

| Figure 4.2: Single-process Gateway                                        | 61 |

| Figure 4.3: Dual-processor with Services Separation                       |    |

| Figure 4.4: Dual-processor with Domain Separation                         | 62 |

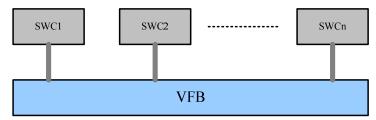

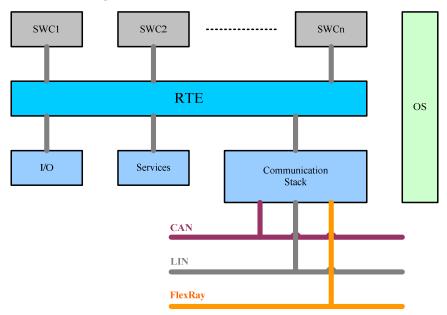

| Figure 4. 5: Software Components in the system communication via the VFB_ |    |

| Figure 4.6: Software Components in the system communication via the VFB   |    |

|                                                                           |    |

|                                                                           | 66 |

| Figure 4.8: HW/SW partitioning of dual processor gateway                  |    |

| Figure 4.9: The Gateway Structure with a Dedicated Hardware               | 0  |

| Figure 4.10: A Basic Gateway Structure                                    | 68 |

| Figure 4.11: Router Management Structure                                  |    |

| Figure 4.12: Router structure with hardware support                       |    |

| Figure 4.13: The Structure of a Hardware Router                           |    |

| Figure 4.14: CAN and FlexRay Communication                                |    |

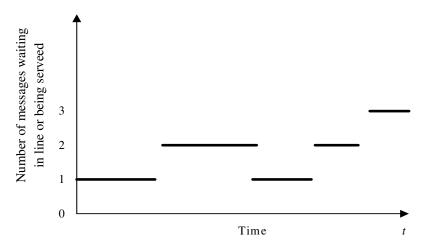

| Figure 5.1: The Example of a Discrete System                              |    |

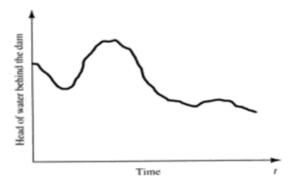

| Figure 5.2: The Example of a Continuous System                            | 77 |

#### **TABLE OF CONTENTS**

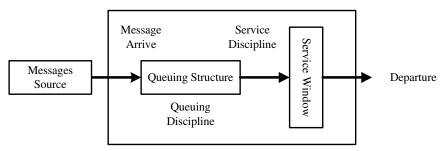

| Figure 5.3: Basic Model of Queuing Process                             | 80      |

|------------------------------------------------------------------------|---------|

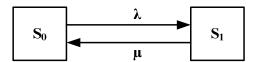

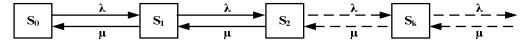

| Figure 5.4: MIMIOIO States                                             | 85      |

| Figure 5.5: MIMI1 States                                               | 86      |

| Figure 5.6: MIMI1Im States                                             | 86      |

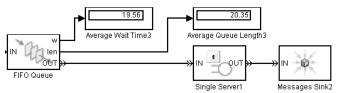

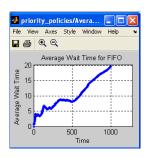

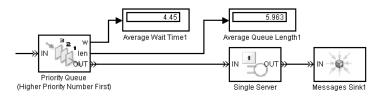

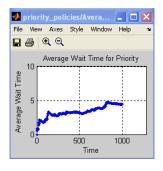

| Figure 5.7: The Example of the FIFO Queue Block                        | 92      |

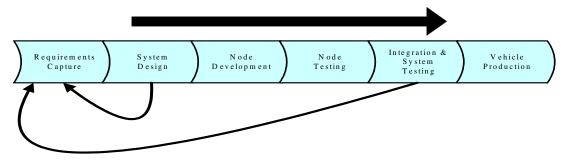

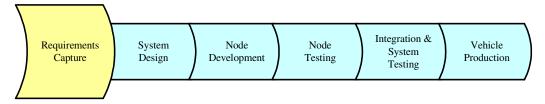

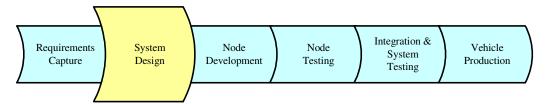

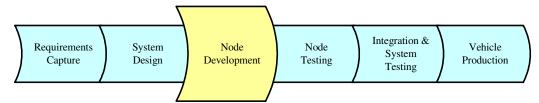

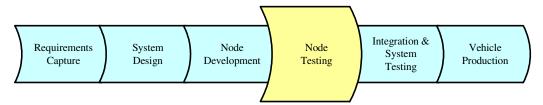

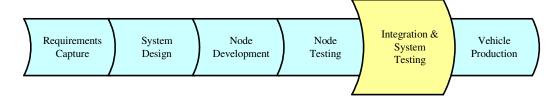

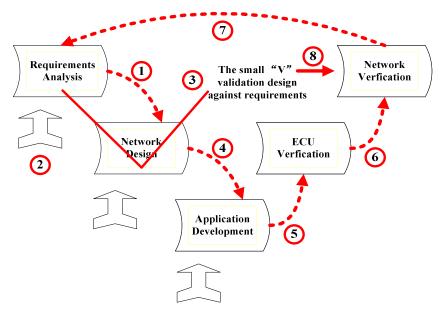

| Figure 7.1: Simulation Process                                         | 100     |

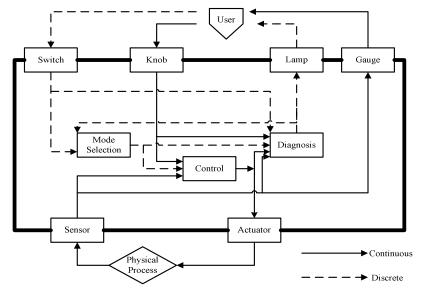

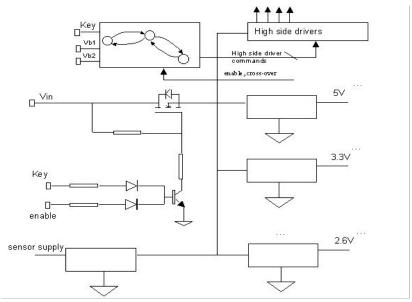

| Figure 8.1: System Architecture                                        | 107     |

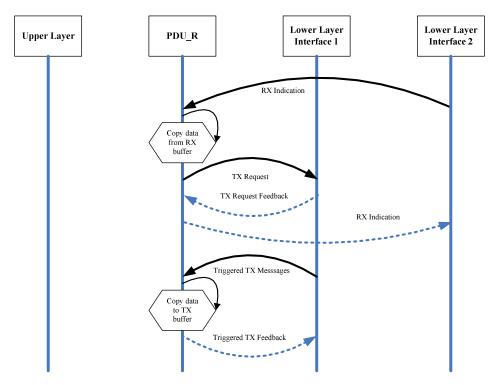

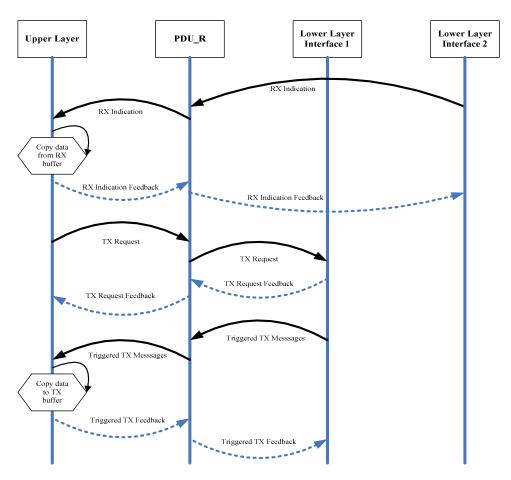

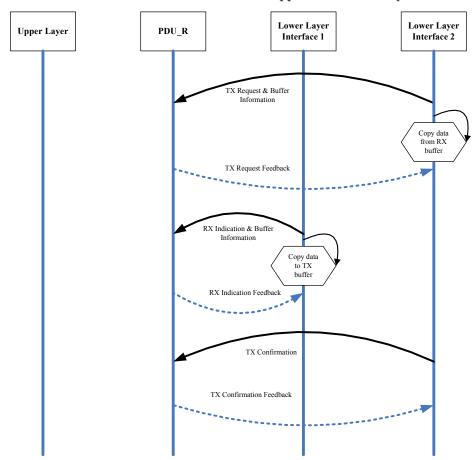

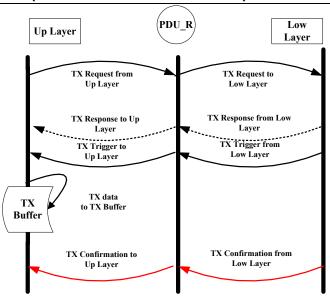

| Figure 8.3: Non TP-PDU-TX without Triggered                            | 110     |

| Figure 8.4: Non TP-PDU-TX with Trigger Transmit                        |         |

| Figure 8.5: TP-PDU-TX                                                  | 112     |

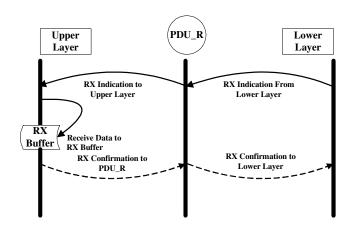

| Figure 8.6: Non TP-PDU-RX                                              |         |

| Figure 8.7: TP-PDU-RX                                                  | 114     |

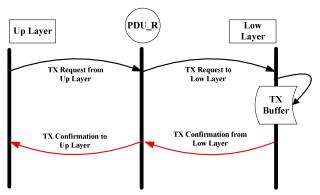

| Figure 8.8: Non TP-PDU-Gateway without Rate Conversion (Non-Triggered) | 115     |

| Figure 8.9: Non TP-PDU-Gateway without Rate Conversion (Triggered)     | 115     |

| Figure 8.10: Non TP-PDU-Gateway with Rate Conversion                   |         |

| Figure 8.11: Gateway Block                                             |         |

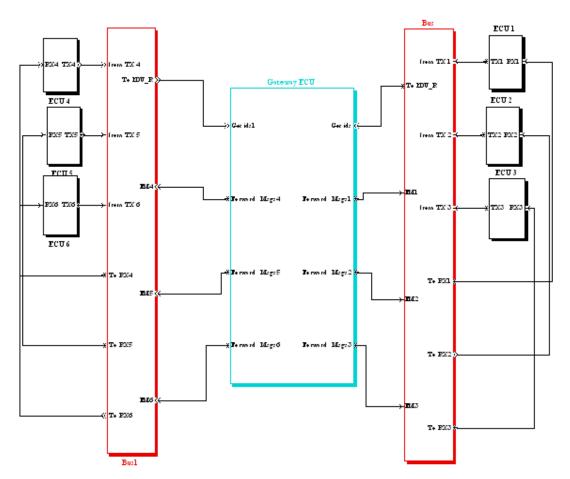

| Figure 9.1: In-vehicle Network Simulation Model                        |         |

| Figure 9.2: Rest Bus Block                                             | 123     |

| Figure 9.3: Single Message Transmission Code                           | 126     |

| Figure 9.4: Formula for Messages per Second                            |         |

| Figure 9.5: Message transmission details                               |         |

| Figure 9.6: Network Status Display                                     |         |

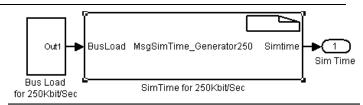

| Figure 9.7: Bus Load for 250 Kbits/Sec Simulations                     |         |

| Figure 9.8: S-Function Builder for simulation time                     |         |

| Figure 9.9: Time Scheduled Messages Transmission                       | 132     |

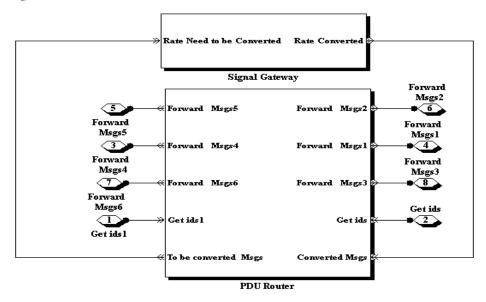

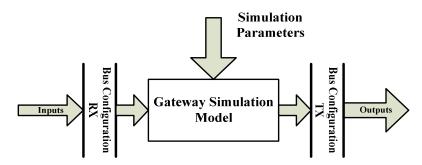

| Figure 9.10: Gateway Block                                             | 133     |

| Figure 9.11: Gateway Simulation Model                                  | 133     |

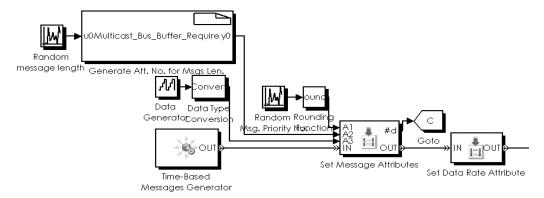

| Figure 9.12: Random Message Generation                                 |         |

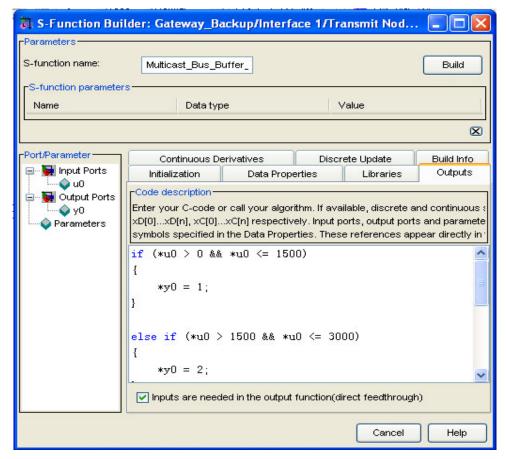

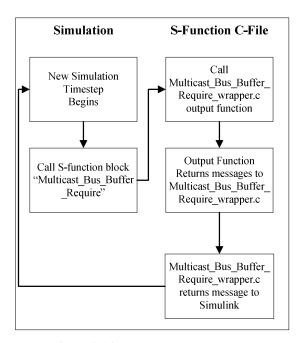

| Figure 9.13: Message Length S-Function                                 |         |

| Figure 9.14: S-Function Process                                        | <br>136 |

| Figure 9.15: Buffer Selection                                          | 136     |

| Figure 9.16: Routing table steps                                       | 138     |

| Figure 9.17: Routing Table Block                                       | 138     |

| Figure 9.18: S-Function Builder for Rate Convert                       | <br>139 |

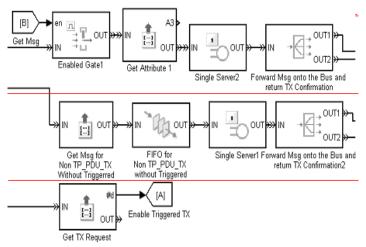

| Figure 9.19: Non Triggered Message Generation                          | <br>140 |

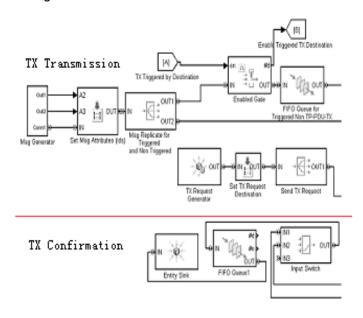

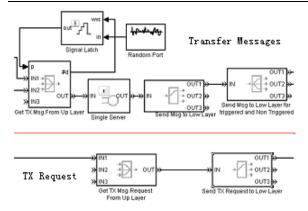

| Figure 9.20: Non-triggered Transmission (TP or Non-TP)                 | 141     |

| Figure 9.21: Triggered Transmission in Gateway Simulation Model        |         |

| Figure 9.22: Triggered Transmission in Receive Node Simulation Model   |         |

| Figure 9.23: Time Scheduled Messages Reception                         |         |

| Figure 10.1: Model Testing                                             | 1 47    |

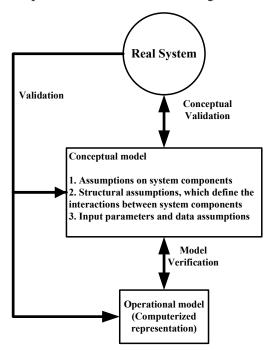

| Figure 10.2: Routing Information Scope                                 | 148     |

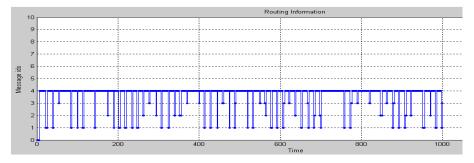

| Figure 10.3: Buffer Selection Scope                                    | 149     |

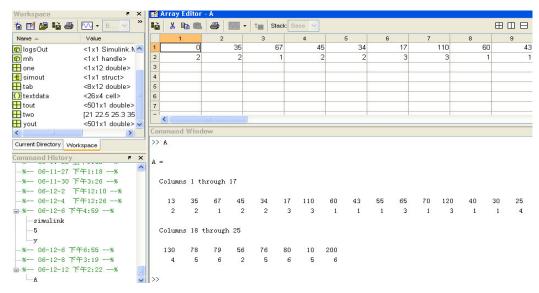

| Figure 10.4: Routing Table Workspace                                   | 149     |

| Figure 10.5: Gateway Validation Procedures                             | 161     |

| g                                                                      |         |

# TABLE OF TABLES

| Table 2.1: Description of FlexRay Static Segment and Dynamic Segment | 25  |

|----------------------------------------------------------------------|-----|

| Table 2.2: Vehicle Network Standard                                  | 26  |

| Table 2.3: FlexRay and CAN Comparison                                | 27  |

| Table 3.1: Example of functions in vehicle                           | 42  |

| Table 4.1: In-vehicle Network Protocol differences                   | 72  |

| Table 5.1: Data Types in Details                                     | 89  |

| Table 5.2: SimEvents Routing Blocks                                  | 92  |

| Table 5.3: SimEvents Routing Techniques                              | 92  |

| Table 9.1: Message Attribute definitions                             | 124 |

| Table 9.2: Function Description                                      | 127 |

| Table 9.3: Messages Transmission Parameter Details                   | 128 |

| Table 9.4: Effective Length of CAN message                           | 129 |

| Table 9.5: Time Schedule Message Identifiers and Periods             | 131 |

| Table 9.6: Attribute Details                                         | 134 |

| Table 9.7: S-Function Input/Output                                   | 134 |

| Table 9.8: Routing table parameter explanations                      | 137 |

| Table 9.9: Example of a routing table                                | 137 |

| Table 10.1: Verification Testing Case Table Components Description   | 150 |

| Table 10.2: Bus Configuration RX                                     | 161 |

| Table 10.3: Gateway Simulation Model                                 | 162 |

| Table 10.4: Bus Configuration TX                                     | 162 |

| Table 10.5: Gateway Model Evaluation Results                         | 163 |

| Table 10.6: Initial Case Setup 1                                     | 164 |

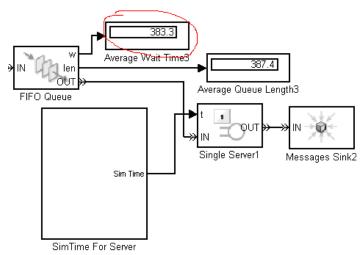

| Table 10.7: Initial Case Setup 2                                     | 168 |

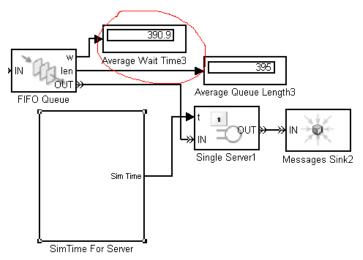

| Table 10.8: Initial Case Setup 3                                     | 172 |

| Table 10.9: Initial Case Setup 4                                     | 176 |

# PART ONE

THESIS OVERVIEW

#### THESIS OVERVIEW

#### 1.1 PROBLEM SPECIFICATION

This aim of this research is to investigate how an in-vehicle network gateway works and how to improve the performance of a gateway optimally.

The automotive industry is entering an exciting and challenging time for electronics system designers. Applications such as infotainment, telemetry, safety, and control require the use of several different networking standards. There are a vast array of networking protocols to choose from, each with advantages and disadvantages. No one protocol satisfies the requirements of all automotive applications.

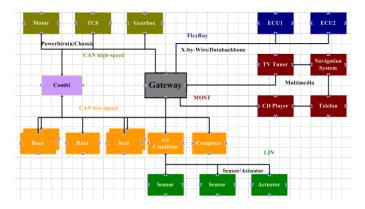

Therefore there is a need to consolidate data from these dispersed networks and feed the relevant processing ECU with the collected data in terms of sending it to its target destination. A gateway is used as a central hub to interconnect and process data from the vehicle's embedded networks. A typical gateway is composed of several automotive networking interfaces such as CAN, Keyword Protocol over CAN, LIN and FlexRay in addition to embedded micro-controllers and peripheral functions.

#### 1.2 SOLUTION REQUIREMENTS

To design an in-vehicle network gateway requires a full understanding of the infrastructure of the whole in-vehicle network, which includes the in-vehicle network protocols, the in-vehicle network management, and the in-vehicle network gateway.

In order to design a reliable gateway, those variations must be accounted for during testing. Even using methodologies such as rapid prototyping, it is difficult to cater for all the critical physical layer permutations that need to be accounted for, therefore simulating a virtual prototype of a gateway is a more effective solution.

#### 1.3 RESEARCH QUESTIONS

The goal of the research is to build a comprehensive gateway simulation model that allows the AUTOSAR gateways performance to be optimised for different networks configurations and bus loads.

The research investigates a number of key questions:

- 1. Which aspects of an AUTOSAR gateway configuration have impact on gateway performance?

- 2. Is the Matlab/Simulink and SimEvents a feasible environment to model and simulate the AUTOSAR defined in-vehicle network gateway system?

- 3. Can a gateway simulation model be used effectively to optimise gateway performance?

#### 1.4 DOCUMENT LAYOUT

The layout of this thesis is as follows:

#### **Chapter 1: Thesis Overview**

This chapter introduces the objectives of this research and the required solutions related to this research. The key research questions are also addressed.

#### **Chapter 2: Vehicle Network Protocols**

This chapter discusses three commonly used in-vehicle network protocols in automotive industry. The differences between these protocols are also discussed in detail.

#### **Chapter 3: Vehicle Network Design**

This chapter introduces the in-vehicle network design process. In this chapter traditional and advanced design processes are compared.

#### **Chapter 4: Network Gateway Design**

This chapter discusses the different requirements for in-vehicle network gateway design from two aspects: hardware and software.

#### **Chapter 5: Simulation**

This chapter outlines some simulation techniques, which are useful for this research. Also in this chapter, a very powerful simulation tool in the automotive industry is introduced.

#### **Chapter 6: Literature Review Summary**

This chapter reviews the existing literature, which has been extensively covered throughout the development of the thesis.

#### **Chapter 7: Methodology**

This chapter describes the methodology used to develop and implement the prototype.

#### **Chapter 8: Gateway Model Requirements Specification**

This chapter presents the in-vehicle network system specification introduced by AUTOSAR. This chapter uses sequence diagrams to show different communication scenarios. The sequence diagrams are grouped into three sections: PDU Reception, PDU Transmission and PDU Gateway.

#### **Chapter 9: Gateway Simulation Model Design**

This chapter describes the in-vehicle network simulation model by using a simulation tool. The simulation model includes: different protocol controllers (time and event triggered), communication bus and gateway.

#### **Chapter Ten: Testing**

This chapter describes the test environment and test cases used to test the system and produce the results. In this chapter two testing stages are carried out: Verification and Validation.

#### **Chapter Eleven: Conclusion**

This chapter provides a summary of the work conducted in the present research, whilst describing how the objectives were met. The potential for future development is also discussed.

# PART TWO

LITERATURE REVIEW

#### **VEHICLE NETWORK PROTOCOLS**

#### 2.1 Introduction

There are more than ten in-vehicle network protocols currently in use in the automotive industry. Generally they are classified into three basic categories based on network speed and functions (Kopetz, 1993):

- Class A Multiplexing is used for convenience features (entertainment, audio, trip computer, etc.) and does not require high bandwidth;

- Class B Multiplexing is used for general information transfer (instrument cluster, vehicle speed, legislated emissions data, etc.) and requires medium speed;

- Class C Multiplexing requires high bandwidth, reliability, and high data integrity (powertrain control, vehicle dynamics, brake by wire, etc.).

CAN is the most widely used of these protocols. The advantages of CAN Bus include high real-time capabilities, operability in a harsh electrical environment, and easy configurability of the overall system. The CAN protocol, which corresponds to the date rates, is used in different automotive control systems. The high-speed data rates of networking controllers are used for some real-time controls such as engine timing and ABS. The low-speed data rates of networking controllers, which make vehicles more comfortable, are for lighting control and air-condition (Etschberger, 2001).

LIN, as a sub-bus of CAN, is an inexpensive serial bus used for distributed body control electronic systems in vehicles. It enables effective communication for smart sensors and actuators, where the bandwidth and versatility of CAN are not required. Typical applications are door control, seats, and climate regulation. LIN bus, offering

fast time to market, flexible design options, low cost and low power consumption, is a cost-effective complement to CAN.

FlexRay is a flexible network communications system, which meets the requirements of high-speed bus systems that are deterministic, fault-tolerant and capable of supporting distributed control systems. FlexRay protocol is designed to meet the key automotive requirements of dependability, availability, flexibility and a high data rate.

#### 2.2 EVENT AND TIME TRIGGERED COMMUNICATION SYSTEMS

As a distributed real time system, an in-vehicle network has two main design approaches: Event triggered and Time triggered the above support the normal data distribution requirements of the vehicle network.

An Event Triggered system controls signals from non-time events occurring outside or inside the system (Kopetz, 1993). In an event triggered system, messages that are event-based are transmitted right after an event and contain information regarding that event. Once an event happens in such systems, the signaling of events from the protocol controller to the micro-controller is made through the use of an interrupt mechanism. During protocol execution, the event triggered system has to make all scheduling and communication decisions dynamically, with the proper functions being executed according to the current event that took place within the network. An event triggered system is responsible for deciding when a message must be sent (Dilger, 1998).

A Time Triggered system has all of its activities initiated by the progression of time. It uses a time division multiple access (TDMA) method to obtain access to the network bus (Kopetz, 1993). This method gives each node a certain amount of time so that they each have specific transmission time in the network. All nodes have a synchronized clock to prevent any node transmitting out of turn, which results in the concept of a shared global time within the system. Therefore, each node in the network decides when a message is to be transmitted according to this global time. All tasks and communication actions within a time triggered system are periodic and state variables are sampled at predefined points in time. A time triggered system is less flexible than an event triggered system, but it is easier to analyze and test (Kopetz, 1993). More details of time triggered system are discussed in the TTCAN Section 2.3.4 in this chapter.

#### 2.3 Controller Area Network – CAN

The section discuses the Controller Area Network (CAN) (Bosch, 1991).

#### 2.3.1 CAN AND THE OSI MODEL

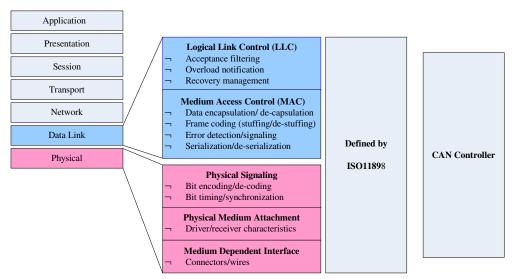

The seven layers of the ISO Open System Interconnection (OSI) (ISO, 1994) model describe most network protocols. Figure 2.1 shows the Data Link Layer and the Physical Layer of the OSI model corresponding to the Control Area Network (CAN) (RICHARDS, 2002).

Figure 2.1: OSI model and layered architecture of CAN

CAN has the following features (Bosch, 1991):

- Multi-master: any node can transmit a message to another node when the CAN bus is free.

- Safety: CAN provides mechanisms for error detection. The CAN bus error rate is less than 4.7\*10<sup>-11</sup>.

- Speed and Distance: when the CAN bus speed is 5KB/s, the furthest distance is 10km; when the CAN bus distance is 40m, the fastest speed is 1MB/s.

- Arbitration: if two or more nodes start transmitting messages at the same time the arbitration mechanism is started.

The CAN specification defines the Data Link Layer. The Logical Link Control (LLC) manages the overload control and notification, message filtering and recovery management functions. The Medium Access Control (MAC) performs the data

encapsulation/de-capsulation, error detection and control, bit stuffing/de-stuffing and the serialization and de-serialization functions.

The International Standards Organization (ISO) has defined a standard, which incorporates the CAN specification and the physical layer. The standard, ISO-11898 (ISO, 1993) was originally created for high-speed in-vehicle communications using CAN. ISO-11898 specifies the physical layer to ensure compatibility between CAN transceivers.

#### 2.3.2 Bus Arbitration

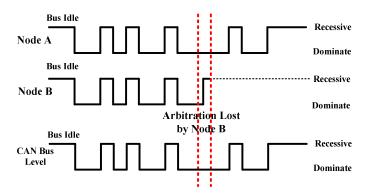

The CAN protocol uses carrier sense multiple access with a collision avoidance (CSMA/CA) mechanism to arbitrate access to the bus (CIA, 2007). It employs a priority mechanism using numerical identifiers to resolve collisions when two or more nodes want to transmit simultaneously. On the CAN bus a zero represents the dominant bit, which is used to overwrite a one (a recessive bit). Therefore, if there are two nodes, one transmitting a one, another transmitting a zero, the bus results in a zero level.

When two or more nodes want to transmit, they monitor the entire bus to check if there is any bus activity. If there is no activity on the bus, they start to transmit their message identifiers (most significant bit first), yet still monitoring the bus levels. If one node transmits a recessive bit on the bus and another transmits a dominant bit, the bus will result in a dominant level. Therefore, the node transmitting a recessive bit will see a dominant bit on the bus (situation where B loses in Figure 2.2) and stop transmitting any further information. In this situation, the node with the lowest number identifier number gains access to the bus and transmits its message. Any node that has lost during the arbitration process then waits until the bus becomes free before re-transmitting its message.

Figure 2.2: CAN bus Arbitration

The CAN protocol uses the bus arbitration mechanism so that the node with the highest priority (lowest value in the identifier field) will continue to transmit without having to back off the bus. It means that CAN has a very predictable behaviour and is very efficient in its use of the bus bandwidth.

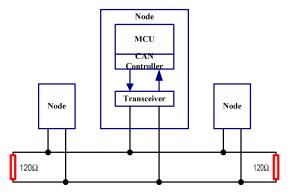

#### 2.3.3 CAN BUS ARCHITECTURE

Figure 2.3 shows an example of a typical CAN bus architecture. Although ISO-11898-2 (ISO, 1993) does not specify the mechanical wires and connectors, this specification does require that the wires and connectors meet the electrical specification. In this specification the data rate is defined up to 1 Mbit/s. The high-speed standard specifies a two-wire differential bus whereby the number of nodes is limited by the electrical bus load. The specification also requires  $120\Omega$  (nominal) terminating resistors at each end of the bus. The common mode voltage ranges from -2V on CAN\_L to +7V on CAN\_H. The nominal specific propagation delay of the two-wire bus line is specified at 5 ns/m. All these figures are valid only for a 1 Mbit/s transfer rate and a maximum network length of 40 m.

Figure 2.3: CAN network according to ISO 11898

#### 2.3.4 Message and Frame Formats

Each CAN message is transferred in the format of a Frame; there are four types of message frames (BOSCH, 1991):

- Data Frame: data is transmitted from a transmitter to one or several receivers.

- Remote Frame: bus nodes (receivers) can request the transmission of a data frame of the same frame identifier by a source.

- Error Frame: signals an error detected by a bus node (transmitter or receiver) and destroys the frame.

- Overload Frame: provides for an extra delay between a preceding and a succeeding data or remote request frame to prevent buffer overruns in a receiver.

The original CAN specifications, that is, Versions 1.0, 1.2, and 2.0A define the message identifier as having a length of 11 bits with the possibility of 2048 different message identifiers. However, the updated version, Version 2.0B extends the identifier's length to 29 bits, which means that both 11 and/or 29 bits can be used.

#### 2.3.4.1 DATA FRAME

In CAN bus communication, data is transmitted from a transmitter to one or several receivers.

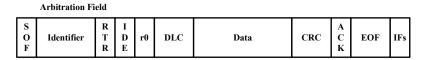

A data frame consists of seven different fields, which are SOF (Start-of-Frame), Arbitration Field (Identifier and RTR), Control Field, Data Field, CRC Field, Acknowledgement Field and EOF (End-of-Frame). Figure 2.4 shows a data frame.

Figure 2.4: Data Frame

#### Start of Frame (SOF)

This bit is the beginning of a data frame, and is represented by a single dominant bit. A bus node is allowed to start bus arbitration only when the bus is idle, and all the nodes have to be synchronized to the leading edge caused by the start bit of the frame.

#### **Arbitration Field**

This field consists of an ID field and a RTR (Remote Transmission Request) bit.

The CAN supports two types of data frame formats: standard frame and extended frame formats. The essential difference between them is the length of the identifier. A CAN standard frame uses 11 bits as the identifier (known as CAN 2.0A), while a CAN extended frame has an identifier with a length of 29 bits (known as CAN 2.0B).

Meanwhile the RTR bit is required to distinguish between the data frame and the remote frame. If a frame is identified as the data frame, the RTR bit takes a dominant value; otherwise the RTR bit is set to recessive. Data frames take precedence over remote frames.

#### **Control Field**

This field consists of an Identifier Extension (IDE) bit, which can be used to distinguish between the CAN standard frame and the CAN extended frame. A reserved bit (r0) is defined as a dominant bit. The Data Length Code (DLC) consists of 4 bits, which are used to specify the number of bytes in the Data field.

#### **Data Field**

A data field has 0~8 bytes, with each byte consisting of 8 bits.

#### **CRC Field**

This field is used to check the integrity of the frame. It consists of a 15 bit CRC sequence for frame checking and a recessively transmitted delimiter bit. The CRC field is calculated by a 15 bit generator polynomial  $(x^{15} + x^{14} + x^{10} + x^8 + x^7 + x^4 + x^3 + 1)$  followed by a recessive CRC delimiter bit.

#### **Acknowledgement Field**

This field consists of the so-called "Acknowledgement Slot" and a succeeding "Acknowledgement Delimiter" bit. In the Acknowledgement Field, the transmitter sends two recessive bits. Correct messages are acknowledged by the receivers by transmitting a dominant bit in the ACK slot regardless of the result of the acceptance test.

#### **EOF**

Every data and remote frame is delimited by a flag sequence of seven recessive bits.

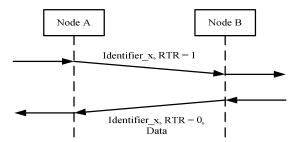

#### **2.3.4.2 REMOTE FRAME**

A remote frame is sent by any node to request a message from another node on the network. Compared to the data frame the remote frame has the RTR bit at the recessive state and contains no data field.

Figure 2.5: Remote Frame

In order to recognise which Data Frame is requested, the initiating node sends a message whose identifier is the same as that of the required Data Frame. Figure 2.5 shows the principle of a data request cycle.

#### 2.3.4.3 Error Frame

Any node detecting a bus error will generate an error frame, which consists of two fields: an Error Flag field and an Error Delimiter field.

The Error Delimiter uses 8 recessive bits to allow the bus nodes to restart bus communications clearly after an error.

The Error Flag (refer to Figure 2.6), of the node detecting the error, decides the content of the Error Flag field. There are two types of error flags: Active Error flag and Passive Error flag.

- If detecting an error in an error state of "error active" on the network, the node will send out an Active Error flag, which is eight dominant bits.

- If detecting an error in error state "error passive" on the network, the node will send out a Passive Error flag, which is eight recessive bits.

#### 2.3.4.4 OVERLOAD FRAME

An overload frame is composed of an overload flag and an overload delimiter. The overload flag consists of a sequence of six consecutive dominant bits. It also destroys the fixed form of the intermission field. As a consequence, all other nodes detect an overload condition, thus they transmit an overload flag.

The overload delimiter consists of eight recessive bits. After transmitting an overload flag every node monitors the bus until it detects a recessive bit. Subsequently every node is finished transmitting its overload flag and all nodes transmit a further seven recessive bits to complete the eight-bit overload delimiter.

#### 2.3.4.5 ERROR DETECTION

The CAN protocol provides the following error detection mechanisms: Bit Check, Frame Check, CRC (Cyclic Redundancy Check), Acknowledgement Check and Stuff Rule Check.

#### 1) Error Types

#### Bit Check

Every transmitting node monitors whether the bus level transmitted differs from the actual level on the bus. If a transmitted bit value is different from the bit value being monitored, a "bit error" is detected.

The overwriting of a recessively transmitted bit level by a dominant level during the arbitration phase as well as during the ACK slot is not interpreted as a bit error. The overwriting of a passive error flag is also not interpreted as a bit error by a transmitting node.

#### Frame Check

If a fixed-form bit field contains one or more illegal bits, a "form error" is detected. A receiver monitoring a dominant bit at the last bit of EOF does not interpret this as a form error.

#### **CRC**

The CRC sequence composed of the CRC calculation results from the transceiver. If the calculated CRC sequence is different from the sequence received, a "CRC error" is detected.

#### Acknowledgement Check

If a transmitter determines that a message has not been acknowledged then a ACK Error is flagged.

#### **Stuff Rule Check**

Bit stuffing is generally used for various purposes:

- Bringing bit streams that do not necessarily have the same or rationally related bit rates to a common rate, or to fill buffers or frames.

- Synchronizing several channels before multiplexing or to rate-match two single channels to each other.

- Limiting the number of consecutive bits of the same value in the data to be transmitted.

In CAN frames, a bit of opposite polarity is inserted after five consecutive bits of the same polarity. This practice is called bit stuffing, and the "Non Return to Zero" (NRZ) coding is adopted. Therefore, in data exchange, six consecutive bits of the same type (111111 or 000000) are considered an error.

Each node detects a violation of the bit-stuffing rule ("stuffing error") as soon as it detects the sixth consecutive bit of equal level in a frame field, which shall be coded by the bit stuffing method.

#### 2) Fault Confinement

Each node on the bus, depending on the Transmit and Receive error counter's values, can be in one of the three states.

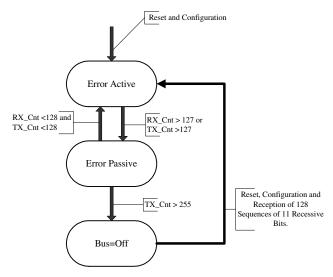

Figure 2.6: Error State Diagram of a CAN node

#### **Error-active**

An "error-active" network node takes part in bus communication and sends an active error flag when it detects an error. This is the default node state at reset.

#### **Error-passive**

An "error-passive" network node has already accumulated a relatively high transmit or receive error count, thus it has monitored a significantly higher error rate over a longer period of time.

#### **Bus-off**

A node in the "bus-off" state is not allowed to have any influence on the bus.

Figure 2.6 shows the error state diagram of a CAN node. After a reset, a node is in the error-active state. If one of the two error counts exceeds the value 127, the monitor demands the MAC sub-layer node enter the error-passive state. A node becomes error

active again when both error counts drop to a below that of 128. A node is disconnected from the bus and is in the bus-off state when the transmit error count exceeds 255. From this state, a node can re-enter the error-active state, with error counts reset to 0, only after reset and reconfiguration and when it has detected 128 sequences of eleven consecutive recessive bits. This measure ensures that a possibly erroneous reset node cannot disturb communication again immediately after reset. Thus up to 128 further frames can be transmitted undisturbed even at a very high busload.

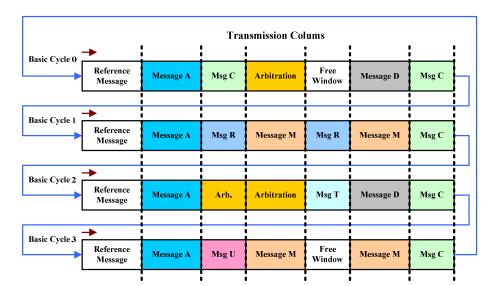

#### 2.3.5 TIME-TRIGGERED CAN (TTCAN)

The communication in the classic CAN network is event triggered; peak loads may occur when the transmission of several messages is requested at the same time (HARTWICH, 2000). CAN uses an arbitration mechanism to ensure that the transmission sequence of all messages corresponds to their identifier priority. However, some mission critical sub-networks within the upcoming generations of vehicle systems, e.g., the x-by-wire system, will require more deterministic behaviour during the communication. For example, when the bus load is at maximum all the safety related messages must still be transmitted. Therefore, it must be possible to allocate a specific amount of time to the message for a high priority transmission. TTCAN is one way to solve the issue.

The time manager in TTCAN communication transmits reference messages regularly. Each individual message to be transmitted is given the time slots in a sequence of time windows following the reference message. There are three types of time windows: Exclusive Time Windows, Arbitrating Time Windows and Free Time Windows.

- Exclusive Time Windows are used for periodic messages.

- Arbitrating Time Windows are used for event messages.

- Free Time Windows are used for future extensions of the network.

The sequence of the time windows is called a basic cycle, which starts with a reference message and contains an off-line configured set of time windows.

Figure 2.7 shows an example of a TTCAN message schedule (Thomas Fuhrer).

Figure 2.7: TTCAN Message Schedule

Basic Cycle is the time between two reference frames. It is not always identical in order to be able to transmit messages at different periodic frequencies. Several basic cycles are repeated in the vehicle network system unless the vehicle is turned off.

Only one node can send a frame during the exclusive window within a basic cycle. There are also free windows and arbitrating windows, for which the nodes compete for bus access, just as in the regular CAN communication. Several arbitrating windows can be merged. The end of an arbitrating window is always predictable.

#### 2.4 LOCAL INTERCONNECT NETWORK – LIN

#### 2.4.1 LIN BUS TECHNICAL OVERVIEW

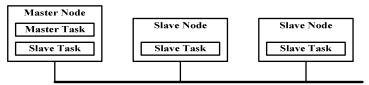

LIN (Local Interconnect Network) (LIN—Consortium, 2003) is a new low cost serial communication system. The communication is based on the SCI (UART) data format, a single-master/multiple-slave concept, a single-wire 12V bus and clock synchronization for nodes without a stabilized time base. Usually, a LIN bus is used in some integration equipment, such as doors, steering wheel, seats and air-conditioning. In these devices, LIN enables a cost-effective communication for smart sensors and actuators. Furthermore, by using digital interface encoding instead of analog interface encoding, electronic devices can be easily connected to in-vehicle network systems and implemented for different diagnosis and maintenance functions including system reprogramming and updating.

#### 2.4.2 LIN PROTOCOL CONCEPT

This section highlights the LIN protocol concept (LIN—Consortium, 2003)

#### **Basic Operation**

LIN bus operation is based on a single-master/multiple-slave concept, as shown in Figure 2.8.

Figure 2.8: LIN bus topology

Each LIN node is divided into two individual parts:

- Master Task, which decides the frame sequence using a schedule table.

- Slave Task, which is responsible for data transfer on the bus, and to allow waking up the entire slave nodes from sleep state.

A typical master node includes a master task and a slave task, but each slave node contains a slave task.

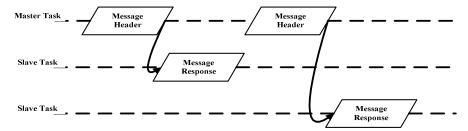

#### **Frame Format**

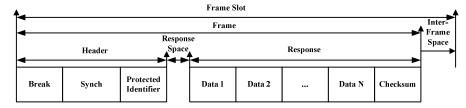

The data unit transferred by a LIN bus is called a data frame. Each frame consists of two parts, as shown in Figure 2.9:

- Message header provided by master task,

- Message response managed by slave task.

Figure 2.9: LIN bus transmission cycle

Each message header comprises the following parts:

- The synchronization break at least 13 dominant bits, sent out by the master task, and included in every LIN frame.

- The synchronization byte -- hex value 0x55, which used to synchronize with the master's clock.

- The message identifier defines unique message content (but not the node address) for receiver side.

The message response of each LIN frame is supplied by a slave task, and it can be divided into Data Field and Checksum, as shown in Figure 2.10:

- Data Field transfers 1~8 bytes of data.

- Checksum computed as inverted eight bit sum with carry.

Figure 2.10: LIN Frame

The data content transferred by message responses in the LIN frame consists of three types:

Signal – the data field of each response includes bits matrix. Under this situation, a frame ID must be between 0x00 and 0x3B.

- Diagnostic information used to transfer diagnostic and configuration data.

This information is 8 bytes long, and has a reserved ID number. ID 0x3C is used by a master request, and 0x3D is used by a slave response.

- Reserved information used for user defined extension, or for the protocol extension. For example, 0x62 is reserved for user addition, and 0x63 is reserved for future improvements of the protocol.

The message headers transferred by a master task are based on a master schedule table. This schedule table defines the transfer sequence of frames and the interval time between frames. The concept of the schedule table is essentially a mechanism which avoids network overload and guarantees data transfer latency.

#### 2.4.3 LIN SPECIFICATION

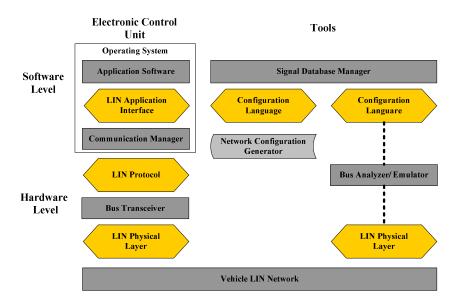

The LIN Standard encompasses the specification (LIN-CONSORTIUM) of the transmission protocol, the transmission medium, the interface between development tools and the interfaces for software programming. LIN guarantees the interoperability of network nodes from the viewpoint of hardware and software and a predictable EMC (Electromagnetic Compatibility) behavior.

The Specification consists of three main parts:

The LIN Protocol Specification describes the Physical Layer and the Data Link Layer of LIN. The main features of the LIN bus are:

- Single master/multiple slave concept (no bus arbitration),

- 0 to 8 byte message frame,

- Data checksum security and error detection,

- Minimum cost for semiconductor components and

- Guarantee of latency times for signal transmission.

The LIN Configuration Language Description describes the format of the LIN configuration file, which is used to configure the complete network and serves as a

common interface between the OEM and suppliers of the different network nodes, as well as an input to the development and analysis tools.

The LIN API describes the interface between the network and the Application Program. This concept allows the implementation of a seamless chain of design and development tools and enhances the speed of development and the reliability of the network.

Figure 2.11: LIN Bus Tool Chain

## 2.5 FLEXRAY

The FlexRay protocol (FLEXRAY-CONSORTIUM, 2000) is the current standard for similar products, which support faster and more highly reliable in-vehicle networks, thus it will lead the whole vehicle electronic control products development for the next generation. FlexRay is the latest in-vehicle network protocol after CAN and LIN, which provides more efficient management for the functionalities of safety and comfort, such as the "X-by-Wire."

FlexRay is a registered trademark of Daimler Chrysler Automotive Group. The FlexRay Consortium promotes the standardization of FlexRay as the next-generation in-car communication protocol.

## 2.5.1 FLEXRAY ADVANTAGES

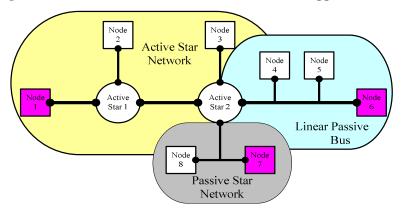

FlexRay (FUJITSU, 2006) focuses on some core requirements including high bit rate, channel redundancy flexible data communication and comprehensive topology, as shown in Figure 2.12.

FlexRay is a type of next-generation in-vehicle network protocol which provide high-reliability and high-speed controls. The CAN network has a speed performance limitation of 1 Mbps, while with a maximum data rate of 10 Mbps available on two channels, giving a gross data rate of up to 20 Mbit/sec, FlexRay can potentially offer 20 times higher bandwidth than a CAN when used in similar applications.

Figure 2.12: FlexRay Topologies

FlexRay has many reliability features that are not available in CAN. For example, a redundant communication capability enables fully duplicated network configurations and schedule monitoring by hardware. Also, FlexRay has flexible configurations, with support for topologies such as bus, star and hybrid types, as shown in Figure 2.12. Designers can configure distributed systems by combining two or more of these topologies. The topologies of FlexRay will be discussed in the next chapter.

In addition, FlexRay allows both synchronous and asynchronous data transfer to meet the demand for various vehicle systems. For example, a distributed control system usually requires synchronous data transmission.

FlexRay provides both static and dynamic communication segments within each communication cycle. The static segment is configured with the fixed time trigger method and the dynamic segment is configured with the flexible event trigger method.

|         | Features            | Slot length<br>/data length | Priorities      | Bus Guardian (BG)           |

|---------|---------------------|-----------------------------|-----------------|-----------------------------|

| Static  | Sends and receives  | Fixed length                | Fixed by        | Because the timing for      |

| Segment | messages with time  |                             | fixed TDMA      | sending is fixed, it is     |

|         | triggers            |                             | protected by BG |                             |

| Dynamic | Sends and receives  | Variable                    | Transmission    | Because the timing of       |

| Segment | messages with event | length                      | in ascending    | sending is undetermined, it |

Table 2.1 below describes each segment.

triggers

Table 2.1: Description of FlexRay Static Segment and Dynamic Segment

order of ID

cannot be protected by BG.

In Table 2.1, a concept called Bus Guardian is applied in FlexRay. The bus guardian (BG) in FlexRay manages the schedules and data independently from the communication controller. The bus guardian monitors timing independently. If a gap in timing is found it sends a signal to prohibit the bus driver from transmitting in order to protect the bus status. Simultaneously, it notifies the host of the error. More details of the bus guardian will be discussed in chapter four "Network Gateway Design."

In addition to operating as a single-channel system similar to CAN and LIN, FlexRay can operate as a dual-channel system. The dual-channel option makes data available via a redundant network – a vital capability for a high-reliability system.

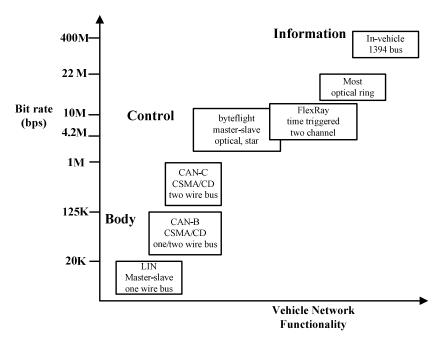

Table 2.2 below shows FlexRay' characteristics meeting real-time control functions.

| Class | Communication  | Applications                                                                | LIN | CAN | FlexRay |

|-------|----------------|-----------------------------------------------------------------------------|-----|-----|---------|

| A     | 10K to 125Kbps | Lamps, lights, door locks, power seats, etc.                                | 1   |     |         |

| В     | 125K to 1Mbps  | Electronic indicators, driving information, automatic air conditioner, etc. |     | 1   |         |

| С     | 1M to 10Mbps   | Engine control, ABS,<br>transmission control, break<br>control, etc.        |     |     | 1       |

Table 2.2: Vehicle Network Standard

Figure 2.13 shows the comparison of networking standards by node cost and data rate.

Figure 2.13: Comparisons of Protocol Data Rates

| Table 2.3 | gives a | detailed | comparison | of FlexRay | and CAN. |

|-----------|---------|----------|------------|------------|----------|

|           |         |          |            |            |          |

| No. | Item                           | CAN                                                                  | FlexRay                                                |

|-----|--------------------------------|----------------------------------------------------------------------|--------------------------------------------------------|

| 1   | Baud rate                      | 1 Mbps                                                               | 10 Mbps                                                |

| 2   | Number of channel for one node | 1 ch                                                                 | 2/1 ch (optional)                                      |

| 3   | Network topology               | Bus type                                                             | Mix. Of bus and star type                              |

| 4   | Connection node (max.)         | 16 nodes at 500 kbps                                                 | 22 nodes (bus) 22/64 nodes (star) 64 nodes (mixed)     |

| 5   | Physical layer                 | Metal                                                                | Metal/POF                                              |

| 6   | Communication                  | Event triggered                                                      | Time triggered, event triggered                        |

| 7   | ID                             | 11/29 bits                                                           | 11 bits                                                |

| 8   | Data length code (DLC)         | 8 bytes                                                              | 254 bytes                                              |

| 9   | Frame                          | Data frame, remote frame, error frame, overload frame                | Data frame                                             |

| 10  | Error status transition        | Error active, error passive, bus off (software restoration possible) | Normal active, normal passive, halt                    |

| 11  | Error counter                  | Status transition counter value fixed                                | Any status transition counter value                    |

| 12  | Types of errors                | Bit error, stuffing error, CRC error, framing error, ACK error       | Clock sync. error                                      |

| 13  | oscillator                     | Ceramic and/or crystal                                               | Crystal oscillator (BG separated from CC clock)        |

| 14  | Network management             | software                                                             | Hardware (controlled by BD and BG)                     |

| 15  | Bus length                     | 40meters at 1 Mbps                                                   | 22 meters (in an active star, and between active star) |

Table 2.3: FlexRay and CAN Comparison

## 2.5.2 FLEXRAY APPLICATIONS

FlexRay was developed for X-by-Wire operation in vehicle networks. Suitable FlexRay applications are:

- EPS (Electronic Power Steering) specifically uses ECUs, it is based on Steering-by-Wire technology.

- ABS (Anti-lock Brake System) includes VSC (Vehicle Stability Control)

and VSA (Vehicle Stability Assist), it is based on Safe-by-Wire technology.

- AT (Automatic Transmission) replaces existing mechanical control systems with computerized fuel injector, computerized variable intake control system, and computerized idling control system. It is based on Drive-by-Wire technology.

## 2.5.3 FLEXRAY PROTOCOL

This section highlights the FlexRay protocol (FLEXRAY-CONSORTIUM, 2000).

## 2.5.3.1 FLEXRAY NODE OPERATION

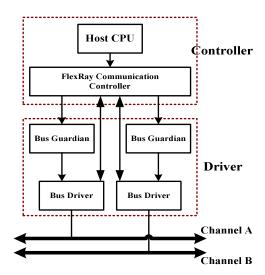

Each FlexRay node consists of a controller part and a driver part (FUJITSU, 2006), as shown in Figure 2.14.

- Controller: includes a host processor and a communication controller.

- Driver: includes bus drivers and optional bus guardians. The bus driver connects the communication controller to the bus, and the bus guardian monitors access to the bus. The host informs the bus guardian which time slots the communication controller is allocated. The bus guardian then allows the communication controller to transmit data only within these time slots thus enabling the bus driver. If the bus guardian detects a gap in the timing it disconnects the communication channel.

Figure 2.14: FlexRay Node

#### **Status Transition**

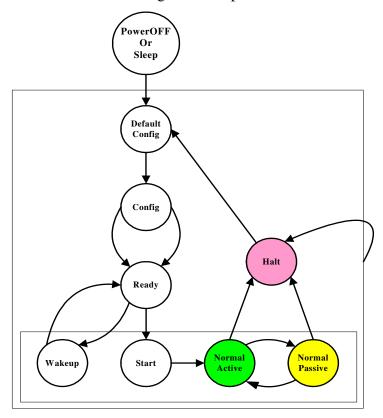

The nodes of FlexRay have the following basic states, as shown in figure 2.15, which vary from the initial setting to normal communication.

- Configuration State (Default config/config) used for different kinds of initial setting, including communication cycle and baud rate.

- Ready State used for internal communication setting.

- Wakeup State –used for waking up the nodes that are not communicating.

Under this state, a node sends out a wakeup signal, wakes up and enables the communication controller, bus driver and bus guardians.

- Startup State used for starting up the clock synchronization and is ready for

communication.

- Normal State used for indicating the communication is ready.

- Halt State used for indicating the interrupt of a communication.

Figure 2.15: FlexRay State Transitions

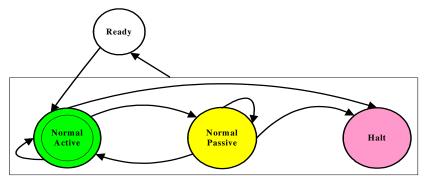

#### **Error State Transition**

The nodes of FlexRay also have an error processing status transition. These status transitions are managed based on an error counter, whose values include a clock synchronization error and clock correction value error depending on the application. When the clock of a node is different to the FlexRay clock synchronisation, a clock synchronisation error is detected. Each FlexRay network has one or more synchronized nodes that transfer synchronisation information. When receiving any synchronisation information, a node will compare its clock with a synchronisation nodes clock and make any necessary changes according to the synchronisation requirements.

Each FlexRay node performs an error count, which counts the number of clock synchronization errors. Nodes monitor the errors related to frame receive and transmit statuses, which consists of the syntax error, content error, bus error and transfer conflict error. Once a signal node detects one of the errors, it informs the Host CPU. The use of an error counter depends on the applications and system design.

Figure 2.16: FlexRay Error State Transitions

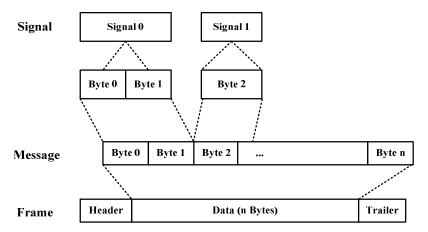

#### 2.5.3.2 Frame Format and Signals

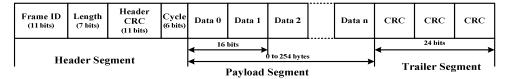

Each communication frame of FlexRay consists of three frame segments: Header Segment, Payload Segment and Trailer Segment, as shown in Figure 2.17.

Figure 2.17: FlexRay frame format

## **Header Segment** includes the following bits:

- Reserved bit used for further expansion.

- Payload preamble indicator indicates the existence of vector information in the payload segment of the frame. In a static frame, this bit indicates NWVector; in a dynamic frame, this bit indicates message ID.

- Null frame indicator indicates whether or not the data frame in the payload segment is NULL.

- Sync frame indicator indicates the existence of a synchronisation frame.

- Start-up frame indicator indicates whether or not the node-sending frame is the start-up node.

- Frame ID assigned to each node at system design.

- Length specifies the data length of the payload segment part.

- Header CRC specifies the CRC calculation values of Sync Frame

Indicator, start-up Frame Indicator, Frame ID and Length that are calculated by the host.

• Cycle – indicates the cycle count of the node that transfers the frame during the frame transfer time.

## Payload Segment includes three parts:

- Data valid range is from 0 to 254 bytes.

- Message ID uses the first two bytes of the payload segment for definition, and it can be used as the filterable data on the receiving side.

- NWVector the network management vector length must be from 0 to 12 bytes and common to all nodes.

**Trailer Segment** includes the CRC value calculated and specified by hardware. It changes the seed value on the connected channel to prevent incorrect connections.

# 2.6 REFERENCES

**BOSCH** (1991) CAN Specification Version 2.0. Stuttgart, Robert Bosch GmbH.

CIA (2007) Controller Area Network (CAN) -- Protocol. ed., CAN in Automation.

**E.DILGER**, T. F., B.MULLER (1998) The X-By-Wire Concept: Time Triggered Information Exchange and Fail Silence Support by new System Services. SAE.

ETSCHBERGER, K. (2001) Controller Area Network. ed. Weingarten, Germany, IXXAT Press.

F.HARTWICH, B. M., T. FUHRER AND R. HUGEL (2000) CAN Network with Time Triggered Communication. CIA (CAN in Automation). Robert Bosch GmbH.

**FLEXRAY-CONSORTIUM** (2000) FlexRay Specification Version 2.1. FlexRay-consortium.

FUJITSU (2006) Next Generation Car Network -- FlexRay. ed., Fujitsu Microelectronics (Shanghai) Co., Ltd.

*H. KOPETZ*, *G. G.* (1993) TTP – A Time Triggered Protocol for Fault-Tolerant Real Time Systems. Proc. 23rd IEEE International Symposium on Fault Tolerant Computing. IEEE Press (pg 524-532).

**ISO** (1993) Road vehicle – Interchange of digital information – Controller Area Network. Huting Verlag, Heidelberg, Germany, International Organization for Standardization.

*ISO* (1994) Information Technology – Open System Interconnection – Basic Reference Model – Conventions for the definition of OSI services. Huting Verlag, Heidelberg, Germany, International Organization for Standardization.

LIN-CONSORTIUM LIN Concept. LIN-consortium.

LIN-CONSORTIUM (2003) LIN Specification Version 2.0. LIN-consortium.

**RICHARDS**, **P.** (2002) A CAN Physical Layer Discussion. ed., Microchip Technology Inc.

**THOMAS FUHRER, B. M.** Time Triggered Communication on CAN (Time Triggered CAN -- TTCAN). CIA (CAN in Automation).

# VEHICLE NETWORK DESIGN

#### 3.1 Introduction

Today's vehicles contain hundreds of circuits, sensors and many other electrical components. Communication is needed in many circuits and functions of the vehicle. In-vehicle networking is a method for transferring data in distributed electronic modules via a serial data bus, such as CAN, LIN and FlexRay. Applying a serial data bus reduces the number of wires by combining the signals on a single wire through time division multiplexing. Information is sent to individual control modules that control each function, such as anti-lock braking, turn signals, and dashboard displays. (NAVET, 2005)

As the electrical equipment of today's vehicles continues to increase, the need for networking is critical. For example, some high-end luxury cars contain more than three miles and nearly 200 pounds of wiring. The resulting number of connectors creates a reliability nightmare. (NAVET, 2005)

#### 3.2 Network Topologies

A network topology structure is a physical layout, which connects different nodes of a communication network. For an in-vehicle network, there are various methods of connection between different protocol nodes, but only few methods can work properly in vehicle networks.

# **Typical Network Topologies**

The most important topologies adopted in vehicle networks are Star, Bus and Ring topologies.

## Star Network Topology (Brown, 1996-2000)

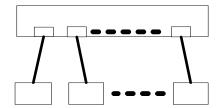

The star network, as shown in Figure 3.1, basically works on a central processor unit, to which all nodes on the network are directly connected. Therefore this central processor unit controls all the information transmission on the network.

Due to its physical structure, a star network has the following advantages and disadvantages:

#### Advantages:

- Each node has its own connection to the central node,

- Simple integration of further nodes and

- Easy to implement with optical transmission media.

#### Disadvantages:

- Generally high total length of all connections if nodes are ordered as a geographical line,

- The central node requires N interfaces for the connection of N nodes,

- Communication between nodes only possible via central node and

- Communication is no longer possible if the central node fails.

Figure 3.1: Star Topology

# **Bus Network Topology** (Brown, 1996-2000)

The bus network, as shown in Figure 3.2, is derived from computer bus access control. It connects all electrically passive nodes to a carrier transfer bus. This topology is also called a "diffusion network," because the data transmitted by one node is available to all nodes. A bus network has the following advantages and disadvantages:

## Advantages:

- Lower cabling costs for applications with nodes geographically ordered as a line,

- Simple connecting of a node,

- Simple extension by further nodes without interruption of the operation,

- Failure or de-activation of one node does not affect the other nodes and

- Arbitrary logical communication structures possible.

#### Disadvantages:

- Limited bus length and number of nodes if signal regeneration by repeaters is not applied,

- Generally, for an electrical bus medium both ends of the bus line have to be terminated by a terminating resistor,

- The implementation of a bus structure with optical media is complicated by the fact that suitable optical branches are still difficult to implement,

- Node identification required.

Figure 3.2: Bus Topology

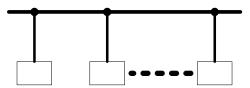

# Ring Topology (Brown, 1996-2000)

A ring topology, as shown in Figure 3.3, is implemented by a closed chain of addressed point-to-point connections.

## Advantages:

- Implementation of extended networks possible because every node provides signal regeneration.

- Suited for the use of optical transmission media due to the applied pointto-point transmission between nodes.

- Simple identification of nodes possible according to the geographic position of the nodes in the ring.

#### Disadvantages:

- Total system fails when one of the nodes fails. Therefore additional

measures are generally taken, e.g. possibility to bridge the failed node or

provision of a redundant ring.

- Operation has to be interrupted for the integration of a new node or replacement of a node.

Figure 3.3: Ring Topology

#### 3.3 NETWORK GATEWAYS

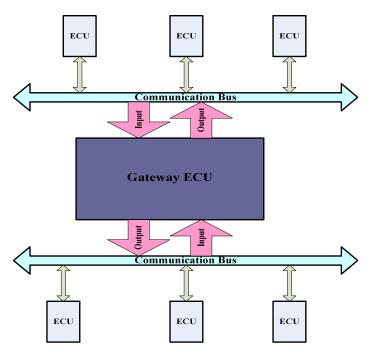

A network gateway is a computer system or device that provides communication between different networks. A gateway is a translator when it uses different network protocols, data formats or languages, even with two systems with different system configurations. A gateway repacks the information received, so that this information can meet system requirements. Meanwhile, a network gateway supplies the functions of filtering and safety. Depending on their implementation, network gateways can operate at the application layer of the OSI model.

Gateways become a critical factor in vehicle network design and applications such as infotainment, telemetry, safety and control which require the use of several networking standards. There are a vast array of networking protocols to choose from – each with advantages and disadvantages. No one protocol satisfies the requirements of all automotive applications. There is a need to consolidate data from these networks and perform processing in a central location. As such, a gateway is used as a central hub to interconnect and process data from a vehicle's embedded networks. A gateway is composed of several automotive networking interfaces such as CAN, LIN and FlexRay, in addition to embedded micro controllers and peripheral functions.

# **General In-vehicle Gateway Types**

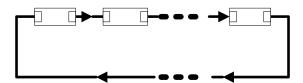

There are three types of gateway used in vehicle networks: Central Gateway (Super Gateway), Multi Gateway and Backbone Gateway. (EASIS, 2005b)

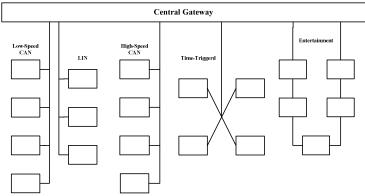

<u>Central Gateways (Super Gateways):</u> provide a single central gateway for different network systems communicating, as shown in Figure 3.4. It is a very sophisticated gateway, which supports very complex functionalities such as connecting all the different bus systems (High-speed bus and low-speed bus), routing information and converting different message formats.

Figure 3.4: Central Gateway

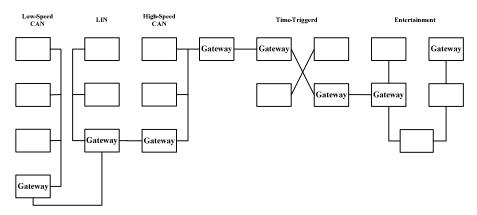

<u>Multi Gateways:</u> are integrated into a single ECU node with the same functionalities as central gateways, as shown in Figure 3.5. It means all communications occurs between ECUs.

Figure 3.5: Multi Gateways

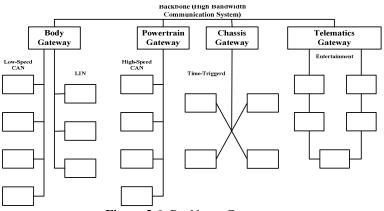

**<u>Backbone Gateways:</u>** performs as a front door for each vehicle sub-network of the whole vehicle network, as shown in Figure 3.6. A high-bandwidth backbone (FlexRay) is required to connect those different sub-networks.

Figure 3.6: Backbone Gateways

## 3.4 NETWORK DESIGN METHODOLOGIES

## 3.4.1 Basic Network Design Methodologies